RM0440 Rev 4 1265/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

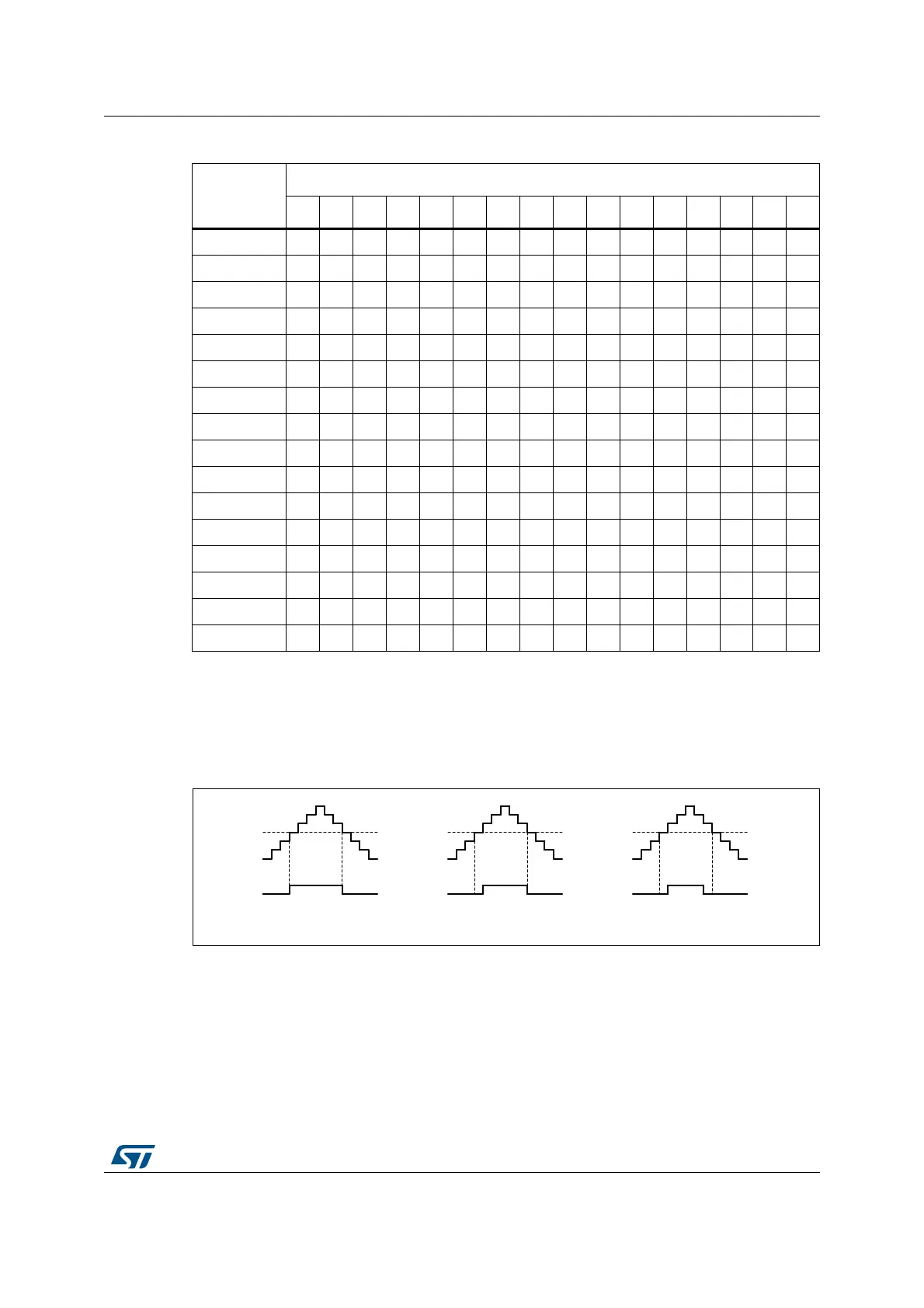

The dithering mode is also available in center-aligned PWM mode (CMS bits in TIMx_CR1

register are not equal to '00'). In this case, the dithering pattern is applied over 8 consecutive

PWM periods, considering the up and down counting phases as shown in the Figure 395

below.

Figure 395. Dithering effect on duty cycle in center-aligned PWM mode

Table 278 below shows how the dithering pattern is added in center-aligned PWM mode.

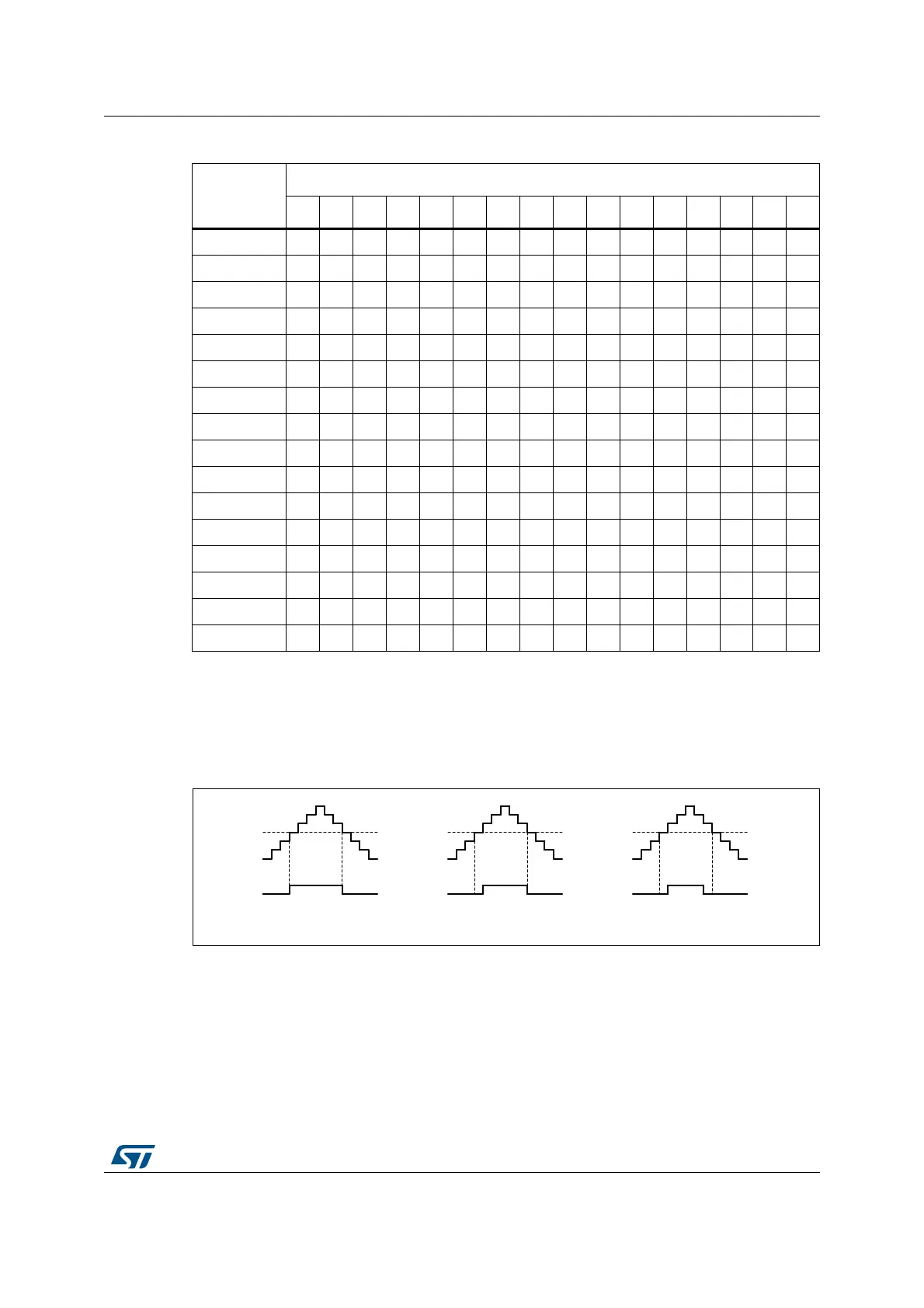

Table 277. CCR and ARR register change dithering pattern

LSB value

PWM period

12345678910111213141516

0000 ----------------

0001 +1---------------

0010 +1-------+1-------

0011 +1---+1---+1-------

0100 +1---+1---+1---+1---

0101 +1-+1-+1---+1---+1---

0110 +1 - +1 - +1 - - - +1 - +1 - +1 - - -

0111 +1 - +1 - +1 - +1 - +1 - +1 - +1 - - -

1000 +1-+1-+1-+1-+1-+1-+1-+1-

1001 +1+1+1 -+1 -+1 -+1 -+1 -+1 -+1 -

1010 +1 +1 +1 - +1 - +1 - +1 +1 +1 - +1 - +1 -

1011 +1+1+1 -+1+1+1 -+1+1+1 - +1 - +1 -

1100 +1 +1 +1 - +1 +1 +1 - +1 +1 +1 - +1 +1 +1 -

1101 +1 +1 +1 +1 +1 +1 +1 - +1 +1 +1 - +1 +1 +1 -

1110 +1+1+1+1+1+1+1 -+1+1+1+1+1+1+1 -

1111 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 +1 -

MSv50904V1

No dithering Dithering up Dithering down

Loading...

Loading...