RM0440 Rev 4 1145/2126

RM0440 Advanced-control timers (TIM1/TIM8/TIM20)

1226

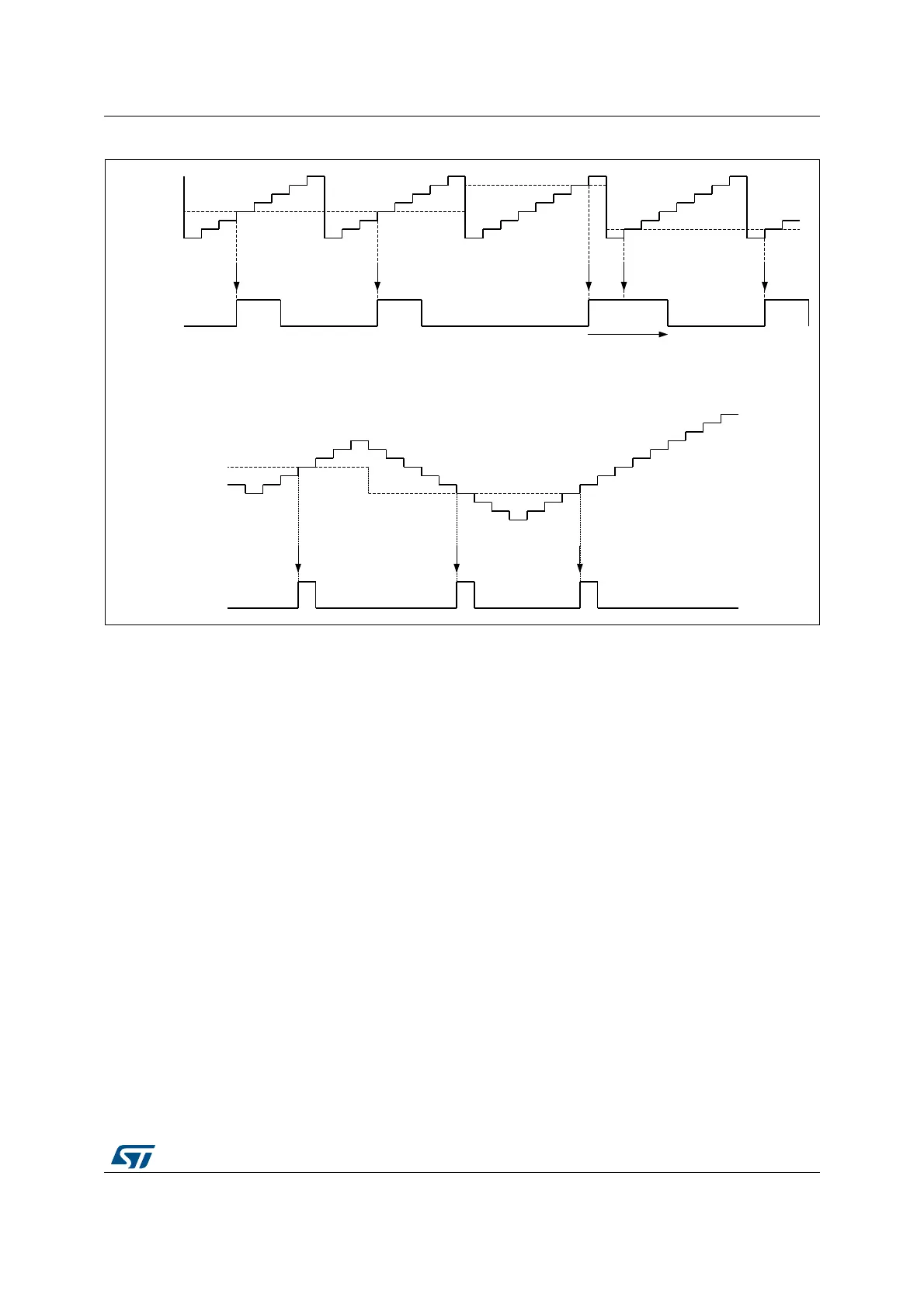

Figure 327. Pulse generation on compare event, for edge-aligned and encoder modes

This output compare mode is selected using the OC3M[3:0] and OC4M[3:0] bit fields in

TIMx_CCMR2 register.

The pulsewidth is programmed using the PW[7:0] bitfield in the register, using a specific

clock prescaled according to PWPRSC[2:0] bits, as follows:

t

PW

= PW[7:0] x t

PWG

where t

PWG

= (2

(PWPRSC[2:0])

) x t

tim_ker_ck

.

gives the resolution and maximum values depending on the prescaler value.

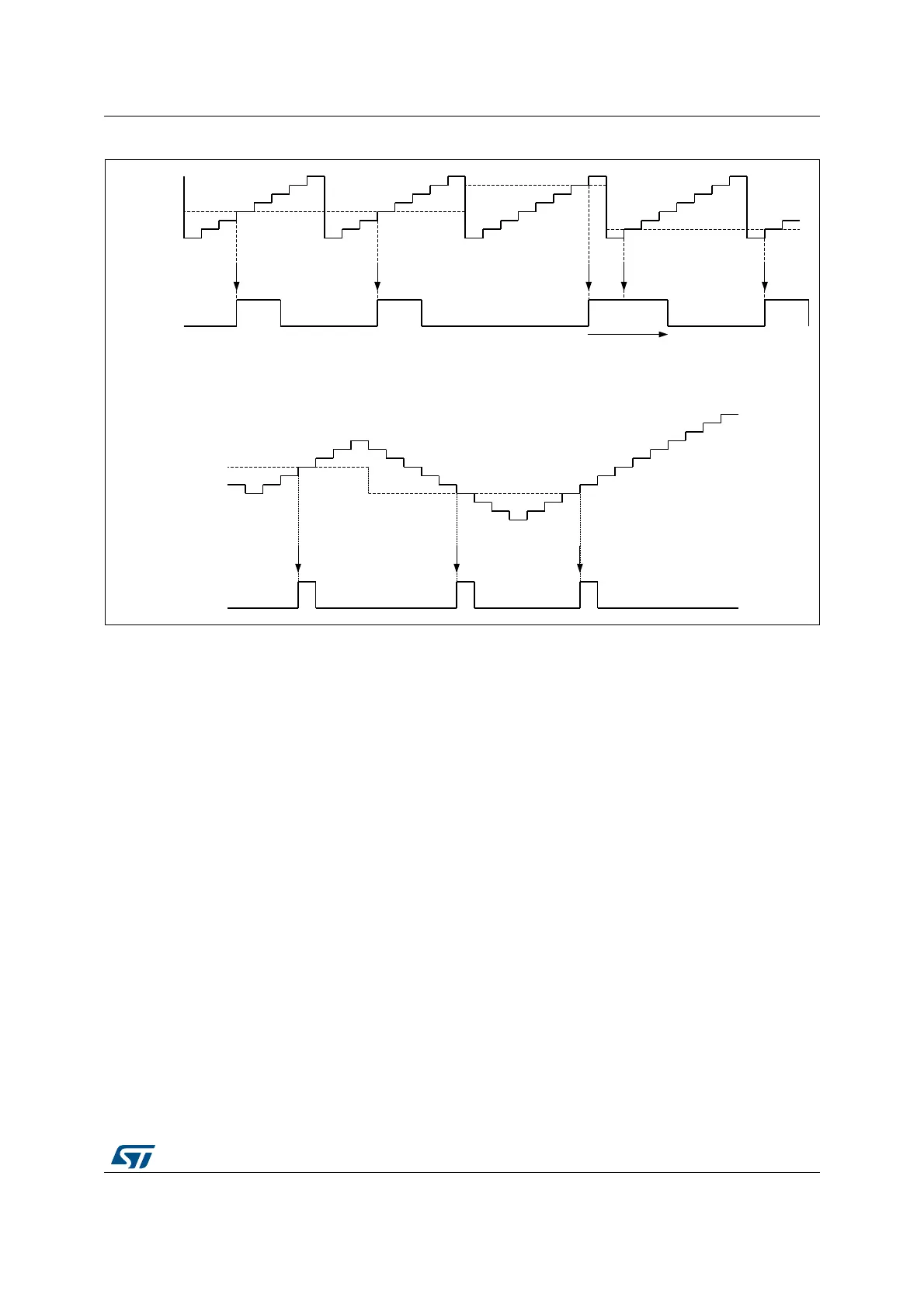

The pulse is retrigerable: a new trigger while the pulse is on-going will cause the pulse to be

extended.

Note: If the two channels are enabled simultaneously, the pulses are issued independently as long

as the trigger on one channel is not overlapping the pulse generated on the concurrent

output. On the opposite, if the two triggers are overlapping, the pulse width related to the 1st

arriving trigger is extended (because of the re-trigger), while the pulse width of the last

arriving trigger is correct (as shown on the Figure 328 below).

MSv62347V1

Extended pulsewidth

due to re-trigger

Counter

CMP3

Triggers

tim_ocx

Counter

CMP3

Triggers

tim_ocx

Loading...

Loading...