RM0440 Rev 4 617/2126

RM0440 Analog-to-digital converters (ADC)

724

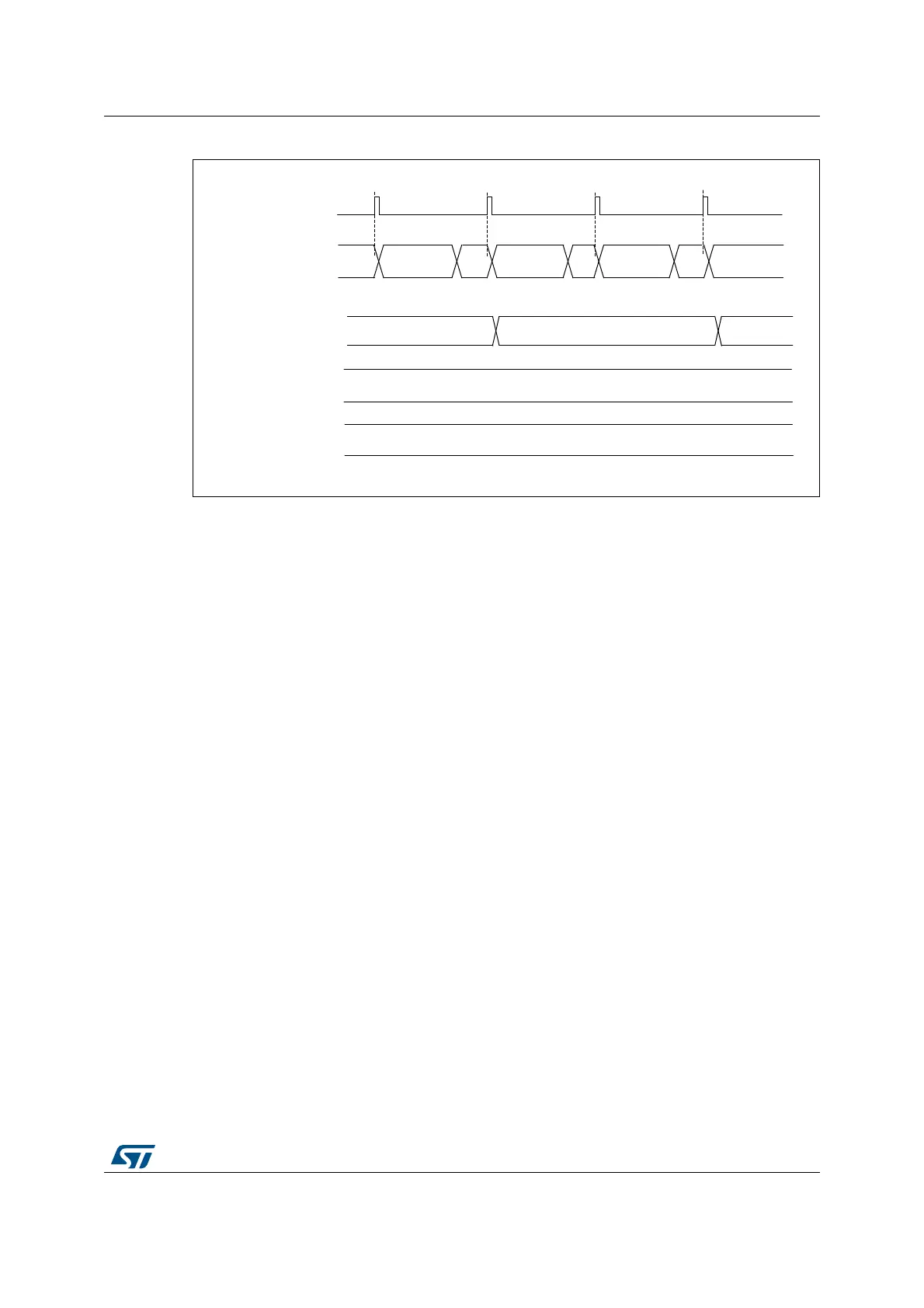

Figure 91. Mixing single-ended and differential channels

21.4.9 ADC on-off control (ADEN, ADDIS, ADRDY)

First of all, follow the procedure explained in Section 21.4.6: ADC Deep-power-down mode

(DEEPPWD) and ADC voltage regulator (ADVREGEN)).

Once DEEPPWD=0 and ADVREGEN=1, the ADC can be enabled and the ADC needs a

stabilization time of t

STAB

before it starts converting accurately, as shown in Figure 92. Two

control bits enable or disable the ADC:

• ADEN=1 enables the ADC. The flag ADRDY will be set once the ADC is ready for

operation.

• ADDIS=1 disables the ADC. ADEN and ADDIS are then automatically cleared by

hardware as soon as the analog ADC is effectively disabled.

Regular conversion can then start either by setting ADSTART=1 (refer to Section 21.4.18:

Conversion on external trigger and trigger polarity (EXTSEL, EXTEN,JEXTSEL, JEXTEN))

or when an external trigger event occurs, if triggers are enabled.

Injected conversions start by setting JADSTART=1 or when an external injected trigger

event occurs, if injected triggers are enabled.

Software procedure to enable the ADC

1. Clear the ADRDY bit in the ADC_ISR register by writing ‘1’.

2. Set ADEN=1.

3. Wait until ADRDY=1 (ADRDY is set after the ADC startup time). This can be done

using the associated interrupt (setting ADRDYIE=1).

4. Clear the ADRDY bit in the ADC_ISR register by writing ‘1’ (optional).

Caution: ADEN bit cannot be set when ADCAL is set and during four ADC clock cycles after the

ADCAL bit is cleared by hardware (end of the calibration).

ADC state

CALFACT_S[6:0] F2

F2

Internal

calibration factor[6:0]

CONV CH 1

CALFACT_D[6:0]

F3

Single ended

inputs channel)

CONV CH3 CONV CH4

(Single inputs

channel)

F3 F2

Trigger event

RDY

RDY RDY

MSv30530V2

CONV CH2

RDY

(Differential

inputs channel)

(Differential

inputs channel)

Loading...

Loading...