Embedded Flash memory (FLASH) for category 3 devices RM0440

122/2126 RM0440 Rev 4

3.5.2 Proprietary code readout protection (PCROP)

Apart of the flash memory can be protected against read and write from third parties. The

protected area is execute-only: it can only be reached by the STM32 CPU, as an instruction

code, while all other accesses (DMA, debug and CPU data read, write and erase) are

strictly prohibited. Depending of the DBANK mode, it allows either to specify one PCROP

zone per bank in dual bank mode or to specify two PCROP zones for all memory. An

additional option bit (PCROP_RDP) allows to select if the PCROP area is erased or not

when the RDP protection is changed from Level 1 to Level 0 (refer to Changing the Read

protection level).

Each PCROP area is defined by a start page offset and an end page offset related to the

physical Flash bank base address. These offsets are defined in the PCROP address

registers Flash PCROP1 Start address register (FLASH_PCROP1SR), Flash PCROP1 End

address register (FLASH_PCROP1ER), Flash PCROP2 Start address register

(FLASH_PCROP2SR), Flash PCROP2 End address register (FLASH_PCROP2ER).

In single bank mode (DBANK=0):

• The PCROPx (x = 1,2) area is defined from the address: base address +

[PCROPx_STRT x 16] (included) to the address: base address +

[(PCROPx_END+1) x 16] (excluded). The minimum PCROP area size is two

2 x double-words (256 bits)

In dual bank mode (DBANK=1)

• The PCROPx (x = 1,2) area is defined from the address: bank “x” base address +

[PCROPx_STRT x 0x8] (included) to the address: bank “x” base address +

[(PCROPx_END+1) x 0x8] (excluded). The minimum PCROP area size is two double-

words (128 bits).

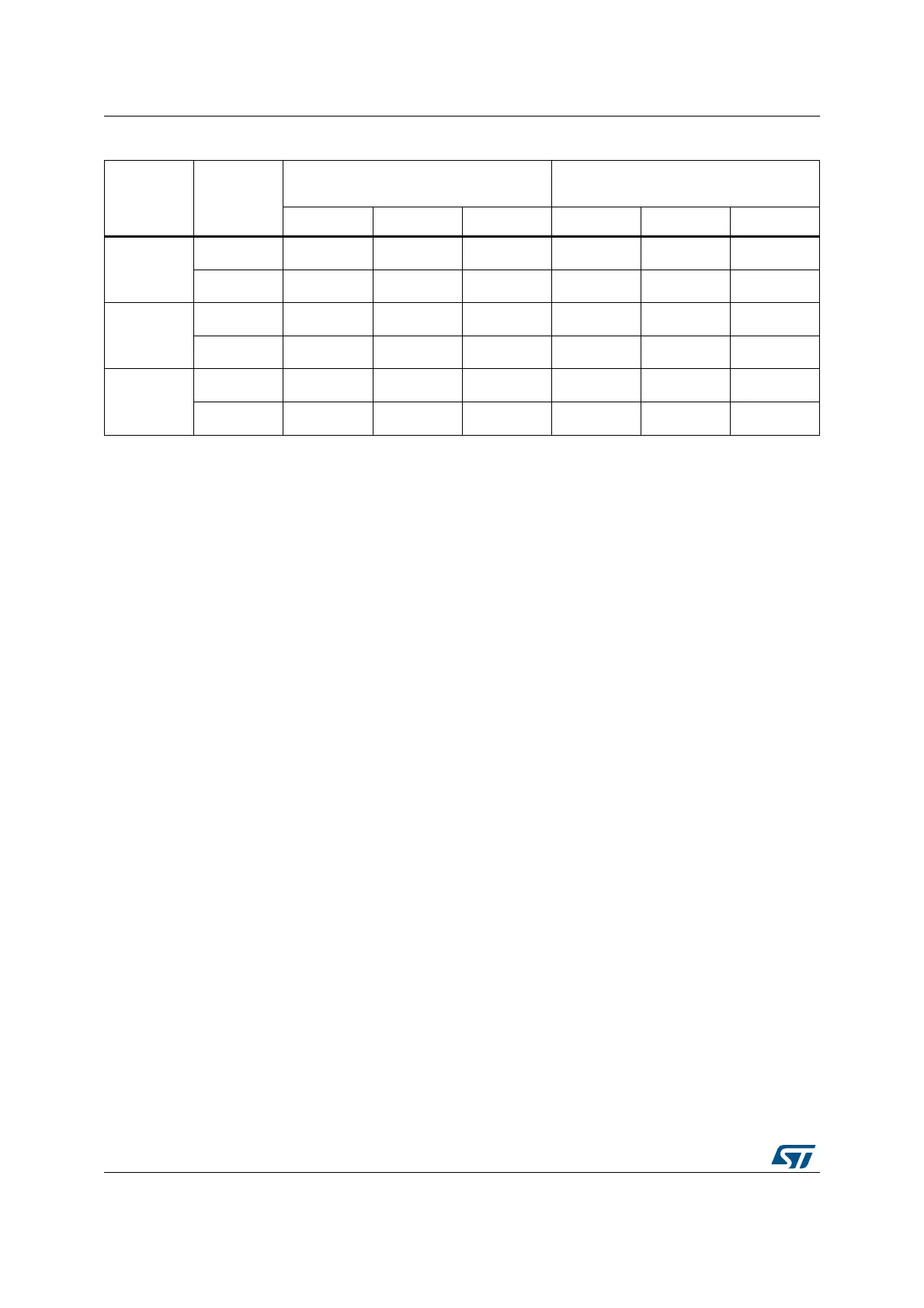

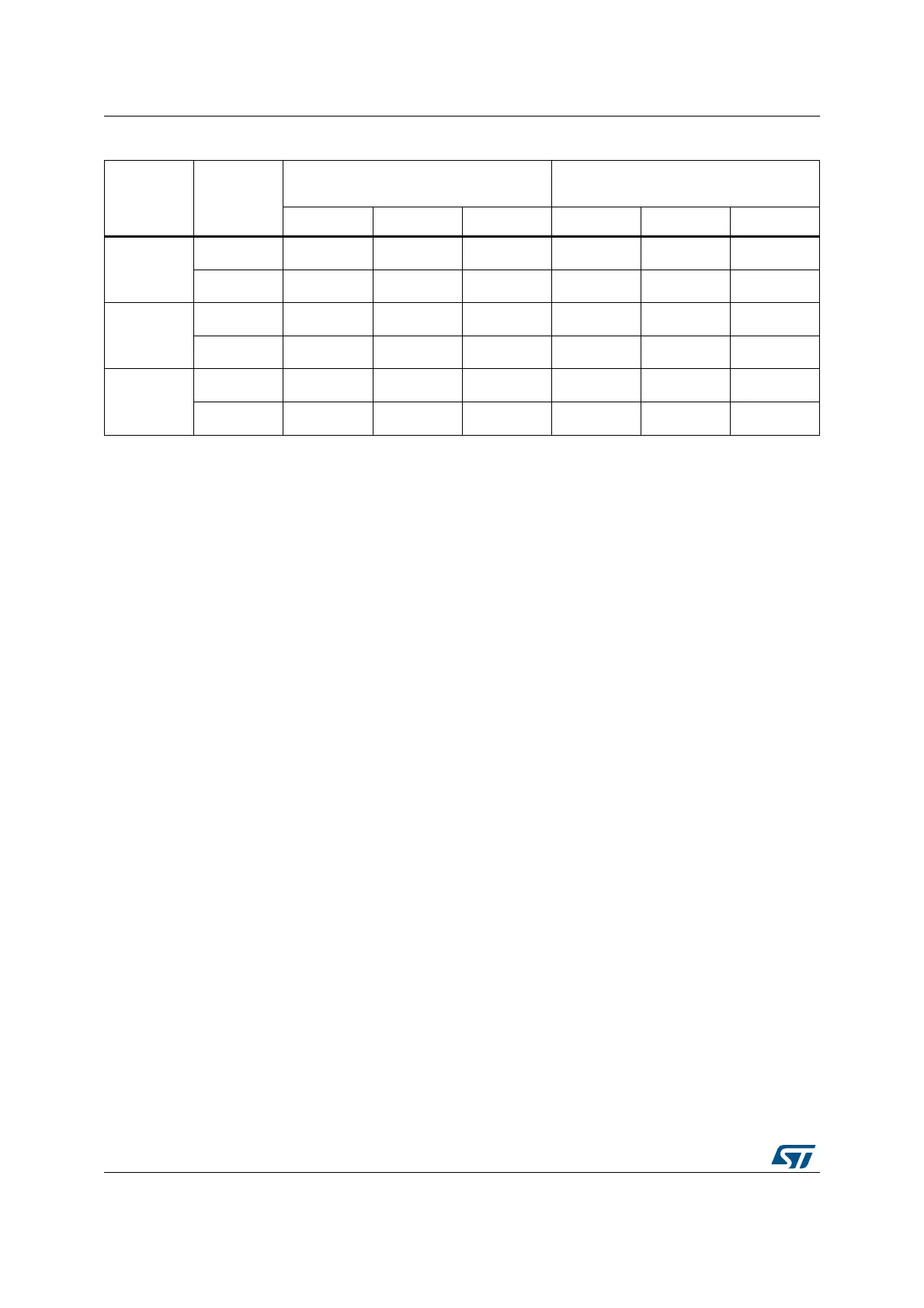

OTP

1 Yes Yes

(4)

N/A No No N/A

2 Yes Yes

(4)

N/A N/A N/A N/A

Backup

registers

1 Yes Yes N/A No No No

(5)

2 Yes Yes N/A N/A N/A N/A

CCM SRAM

1 Yes Yes N/A No No No

(6)

2 Yes Yes N/A N/A N/A N/A

1. When the protection level 2 is active, the Debug port, the boot from RAM and the boot from system memory are disabled.

2. The system memory is only read-accessible, whatever the protection level (0, 1 or 2) and execution mode.

3. The Flash main memory is erased when the RDP option byte is programmed with all level protections disabled (0xAA).

4. OTP can only be written once.

5. The backup registers are erased when RDP changes from level 1 to level 0.

6. The CCM SRAM is erased when RDP changes from level 1 to level 0.

Table 13. Access status versus protection level and execution modes (continued)

Area

Protection

level

User execution (BootFromFlash)

Debug/ BootFromRam/

BootFromLoader

(1)

Read Write Erase Read Write Erase

Loading...

Loading...