RM0440 Rev 4 1623/2126

RM0440 Universal synchronous/asynchronous receiver transmitter (USART/UART)

1733

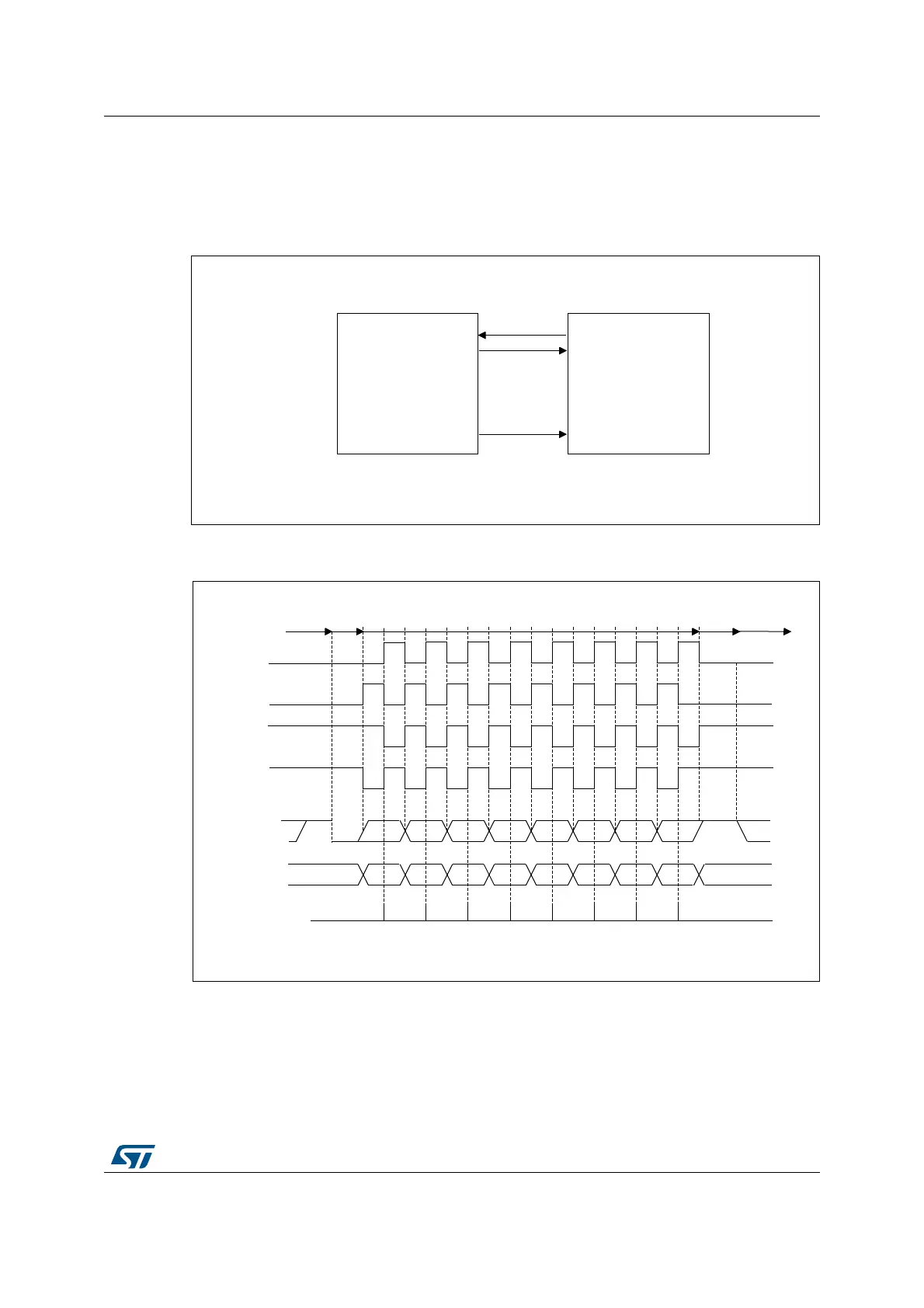

Note: In master mode, the SCLK pin operates in conjunction with the TX pin. Thus, the clock is

provided only if the transmitter is enabled (TE=1) and data are being transmitted

(USART_TDR data register written). This means that it is not possible to receive

synchronous data without transmitting data.

Figure 542. USART example of synchronous master transmission

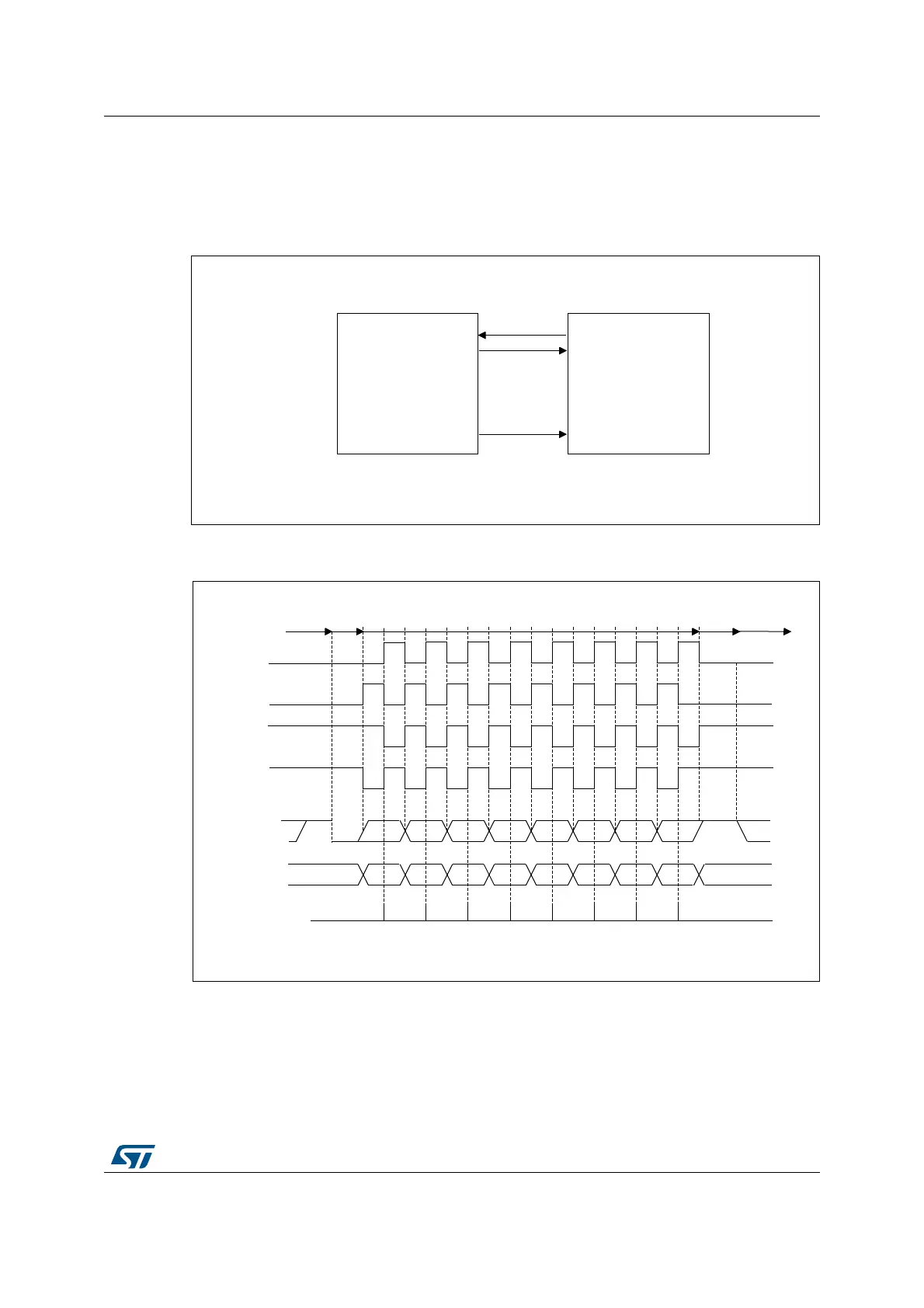

Figure 543. USART data clock timing diagram in synchronous master mode

(M bits =00)

MSv31158V1

USART

Synchronous device

(e.g. slave SPI)

RX

TX

Data out

Data in

Clock

SCLK

MSv34709V2

0 1 2 3 4 5 6 7

0 1 2 3 4 5 6 7

*

*

*

*

MSB

MSB

LSB

LSB

Start

Start Stop

Idle or preceding

transmission

Idle or next

transmission

*

*LBCL bit controls last data pulse

Capture strobe

Data on RX

(from slave)

Data on TX

(from master)

Clock (CPOL=1, CPHA=1)

Clock (CPOL=1, CPHA=0)

Clock (CPOL=0, CPHA=1)

Clock (CPOL=0, CPHA=0)

Stop

M bits = 00 (8 data bits)

Loading...

Loading...