Tamper and backup registers (TAMP) RM0440

1580/2126 RM0440 Rev 4

36.3.2 TAMP pins and internal signals

The TAMP kernel clock is usually the LSE at 32.768 kHz although it is possible to select

other clock sources in the RCC (refer to RCC for more details). Some detections modes are

not available in some low-power modes or V

BAT

when the selected clock is not LSE (refer to

Section 36.4: TAMP low-power modes for more details.

36.3.3 TAMP register write protection

After system reset, the TAMP registers (including backup registers) are protected against

parasitic write access by the DBP bit in the power control peripheral (refer to the PWR

power control section). DBP bit must be set in order to enable TAMP registers write access.

Table 337. TAMP input/output pins

Pin name Signal type Description

TAMP_INx (x = pin index) Input Tamper input pin

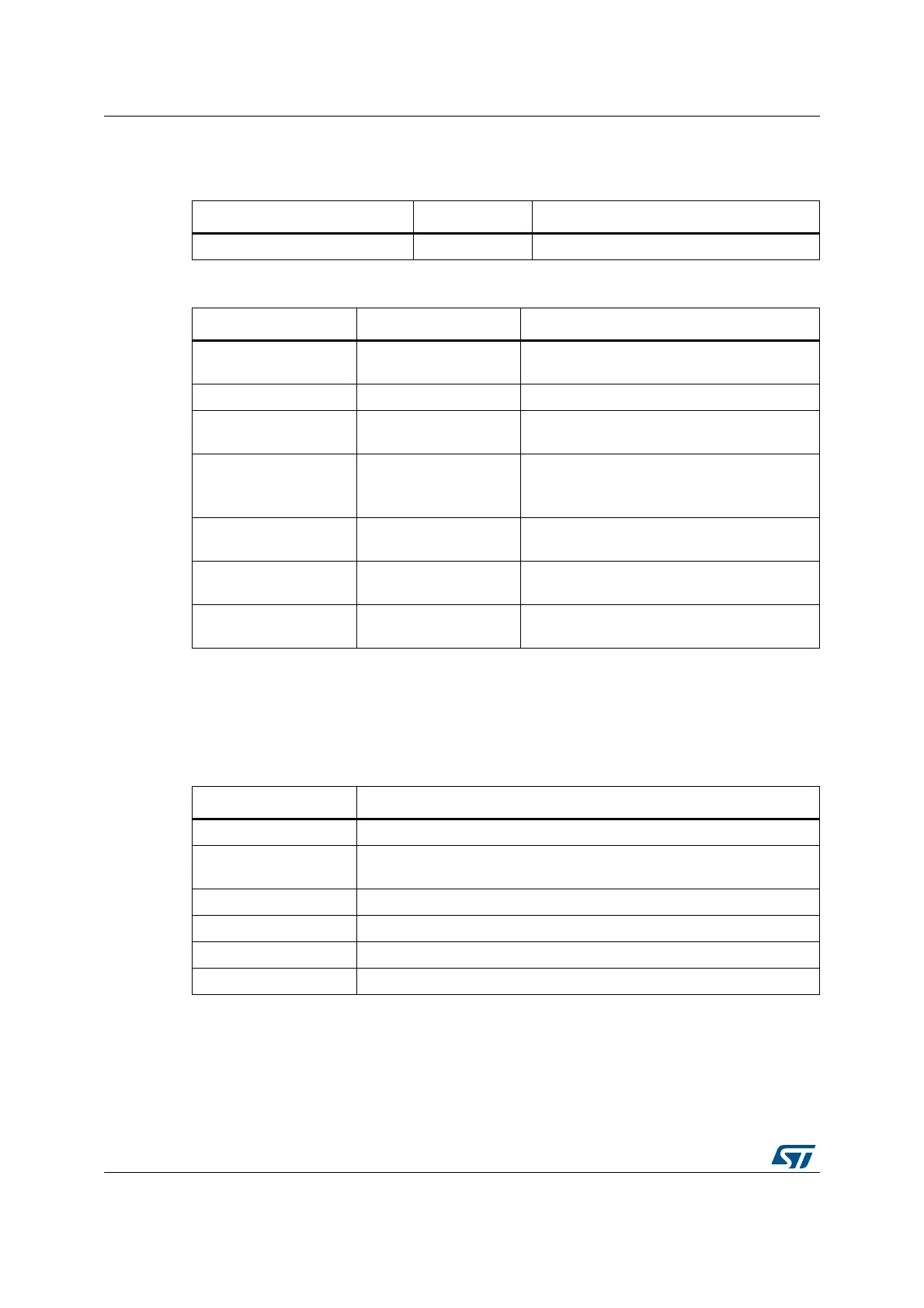

Table 338. TAMP internal input/output signals

Internal signal name Signal type Description

tamp_ker_ck Input

TAMP kernel clock, connected to rtc_ker_ck

and also named RTCCLK in this document

tamp_pclk Input TAMP APB clock, connected to rtc_pclk

tamp_itamp[y]

(y = signal index)

Inputs Internal tamper event sources

tamp_evt Output

Tamper event detection (internal or external)

The tamp_evt is used to generate a RTC

timestamp event

tamp_erase Output

Device secrets erase request following tamper

event detection (internal or external)

tamp_it Output

TAMP interrupt (refer to Section 36.5: TAMP

interrupts for details)

tamp_trg[x]

(x = signal index)

Output Tamper detection trigger

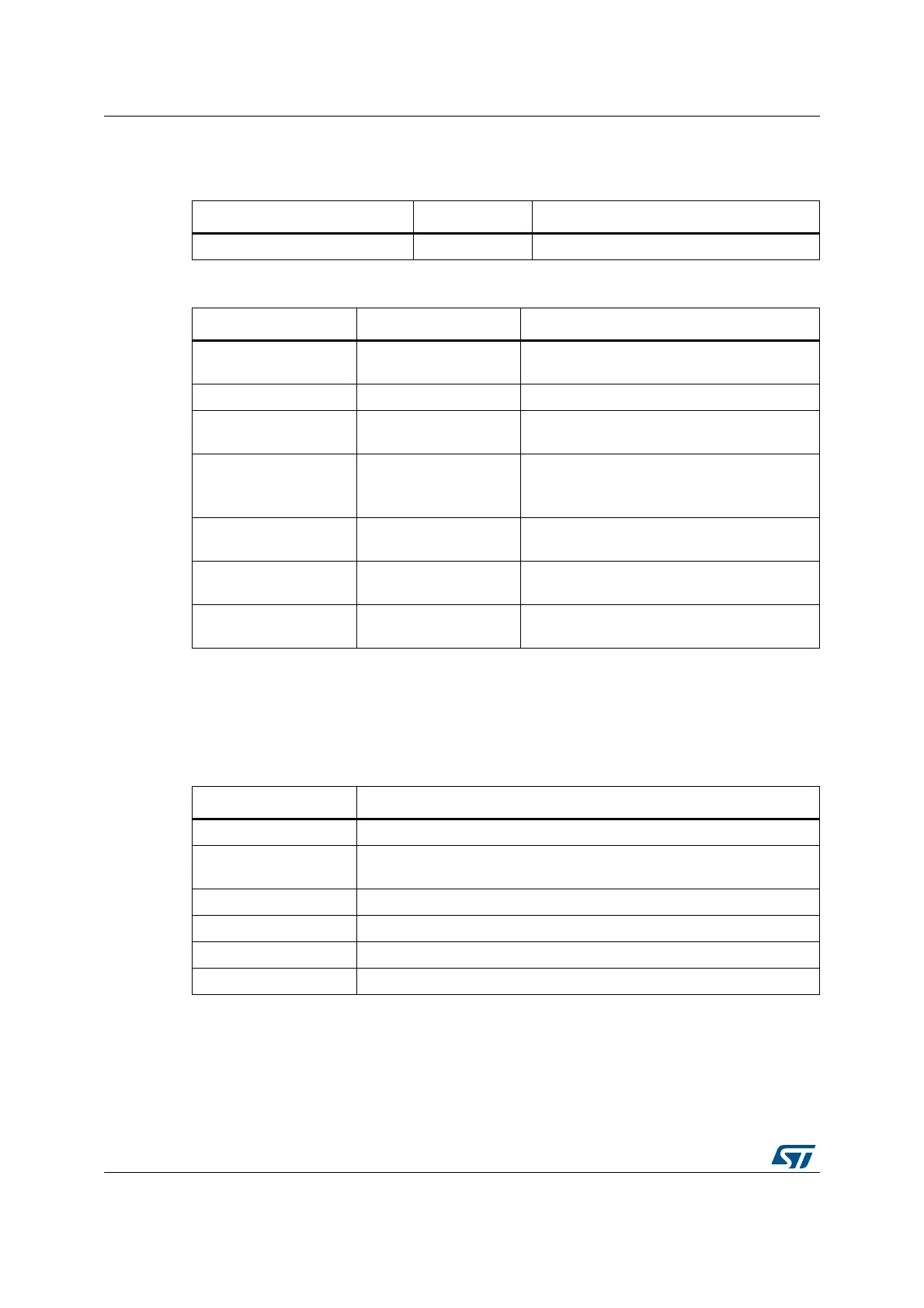

Table 339. TAMP interconnection

Signal name Source/Destination

tamp_evt rtc_tamp_evt used to generate a timestamp event

tamp_erase

The tamp_erase signal is used to erase the device secrets listed

hereafter: backup registers

tamp_itamp3 LSE monitoring

tamp_itamp4 HSE monitoring

tamp_itamp5 RTC calendar overflow (rtc_calovf)

tamp_itamp6 ST manufacturer readout

Loading...

Loading...