RM0440 Rev 4 937/2126

RM0440 High-resolution timer (HRTIM)

1083

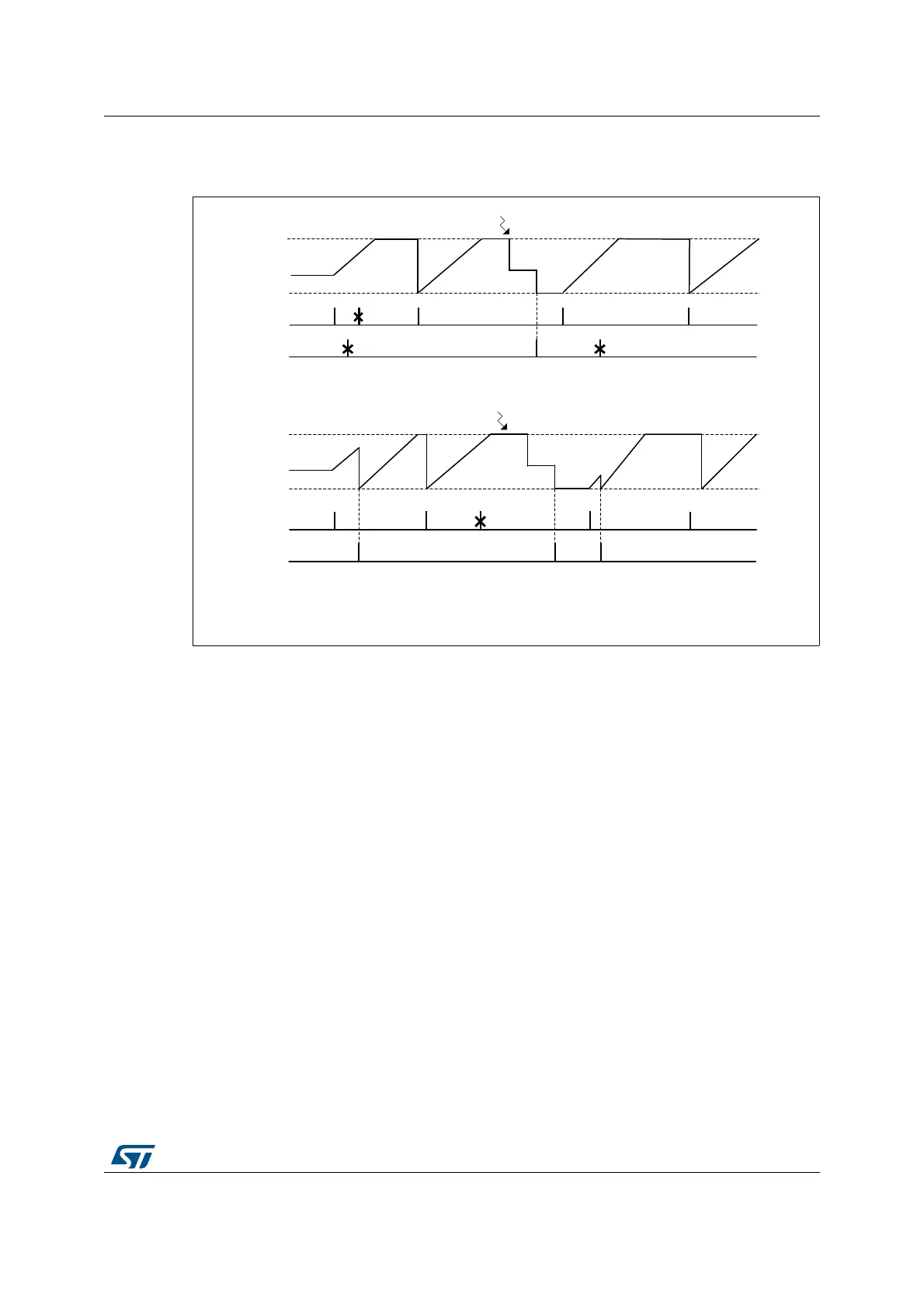

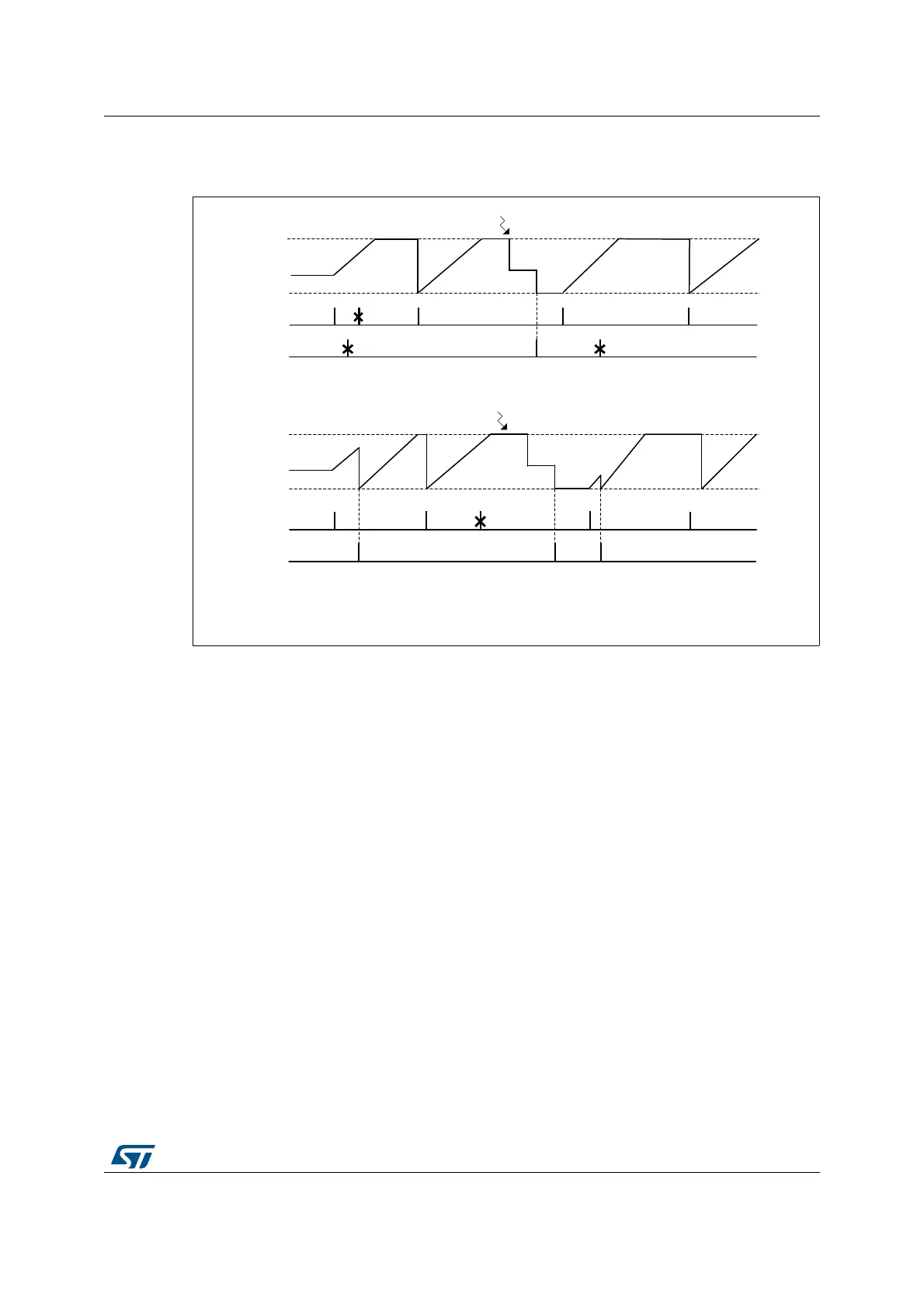

Figure 250 presents how the synchronized start is done in single-shot mode.

Figure 250. Counter behavior in synchronized start mode

27.3.20 ADC triggers

The ADCs can be triggered by the master and the 6 timing units.

10 independent triggers are available for both the regular and the injected sequencers of the

ADCs. The external events can be used as triggers. They are taken right after the

conditioning defined in the HRTIM_EECRx registers, and are not depending on the EEFxR1

and EEFxR2 register settings.

Up to 32 events can be combined (ORed) for ADC triggers 1 to 4, in HRTIM_ADC1R to

HRTIM_ADC4R registers, as shown on Figure 251. The ADC triggers 1/3 and 2/4 are using

the same source set. A multiple triggering is possible within a single switching period by

selecting several sources simultaneously. A typical use case is for a non-overlapping

multiphase converter, where all phases can be sampled in a row using a single ADC trigger

output.

MS32337V1

Counter

PER

SYNCSTRT, Single-shot mode, non-retriggerable

SYNCSTRT, Single-shot mode, retriggerable

Internal reset

request

Counter initialized by software

SCIN

Counter

PER

Internal reset

request

Counter initialized by software

SCIN

Loading...

Loading...