RM0440 Rev 4 1735/2126

RM0440 Serial peripheral interface / integrated interchip sound (SPI/I2S)

1791

39.3 I2S main features

• Half-duplex communication (only transmitter or receiver)

• Master or slave operations

• 8-bit programmable linear prescaler to reach accurate audio sample frequencies (from

8 kHz to 192 kHz)

• Data format may be 16-bit, 24-bit or 32-bit

• Packet frame is fixed to 16-bit (16-bit data frame) or 32-bit (16-bit, 24-bit, 32-bit data

frame) by audio channel

• Programmable clock polarity (steady state)

• Underrun flag in slave transmission mode, overrun flag in reception mode (master and

slave) and Frame Error Flag in reception and transmitter mode (slave only)

• 16-bit register for transmission and reception with one data register for both channel

sides

• Supported I

2

S protocols:

–I

2

S Philips standard

– MSB-justified standard (left-justified)

– LSB-justified standard (right-justified)

– PCM standard (with short and long frame synchronization on 16-bit channel frame

or 16-bit data frame extended to 32-bit channel frame)

• Data direction is always MSB first

• DMA capability for transmission and reception (16-bit wide)

• Master clock can be output to drive an external audio component. Ratio is fixed at

256 × F

S

(where F

S

is the audio sampling frequency)

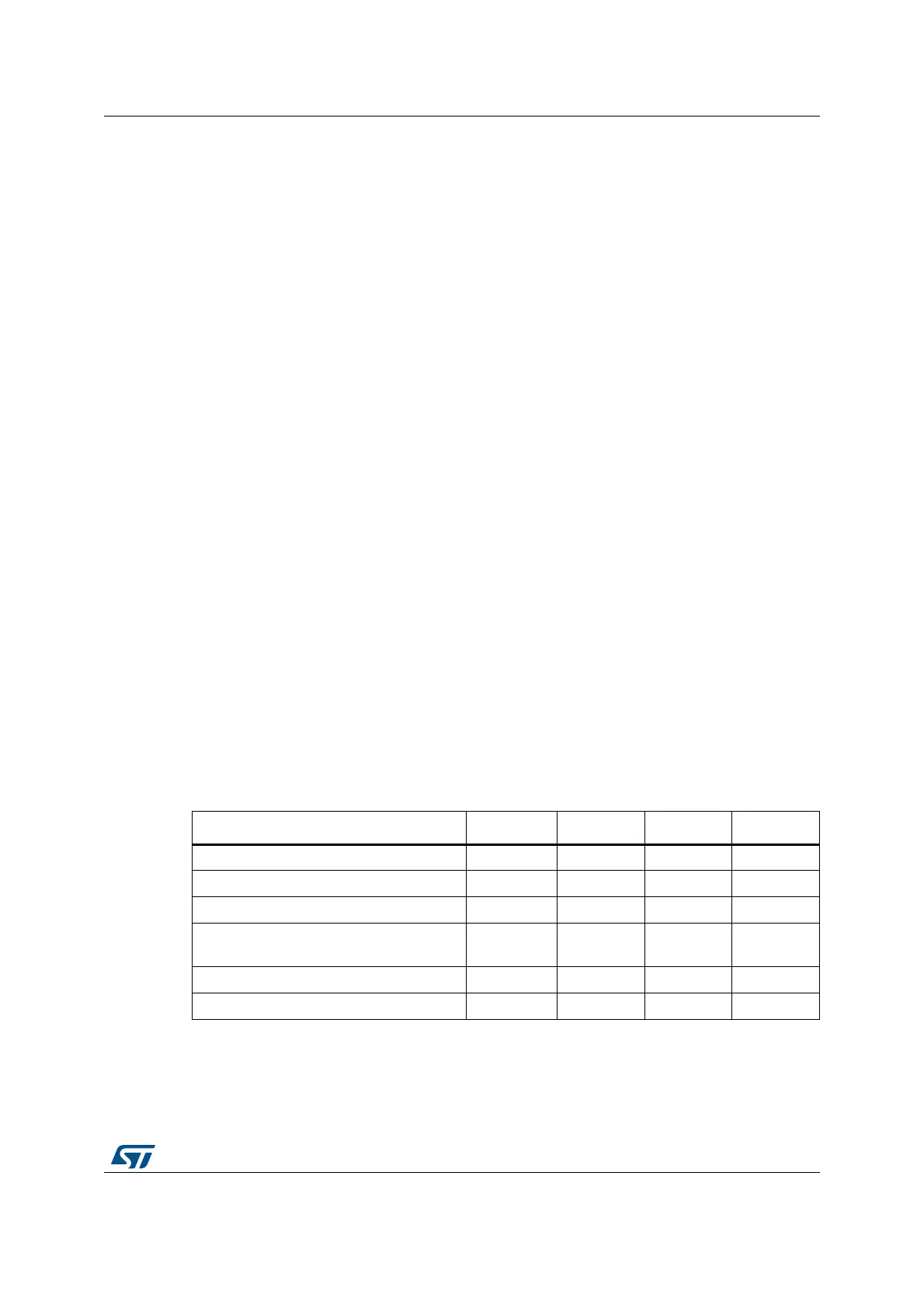

39.4 SPI/I2S implementation

The following table describes all the SPI instances and their features embedded in the

devices.

Table 357. STM32G4 Series SPI and SPI/I2S implementation

SPI features SPI1 SPI2S2 SPI2S3 SPI4

Enhanced NSSP & TI modes Yes Yes Yes Yes

Hardware CRC calculation Yes Yes Yes Yes

I2S support No Yes Yes No

Data size configurable

from 4 to 16-

bit

from 4 to 16-

bit

from 4 to 16-

bit

from 4 to 16-

bit

Rx/Tx FIFO size 32-bit 32-bit 32-bit 32-bit

Wakeup capability from Low-power Sleep Yes Yes Yes Yes

Loading...

Loading...