RM0440 Rev 4 1277/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

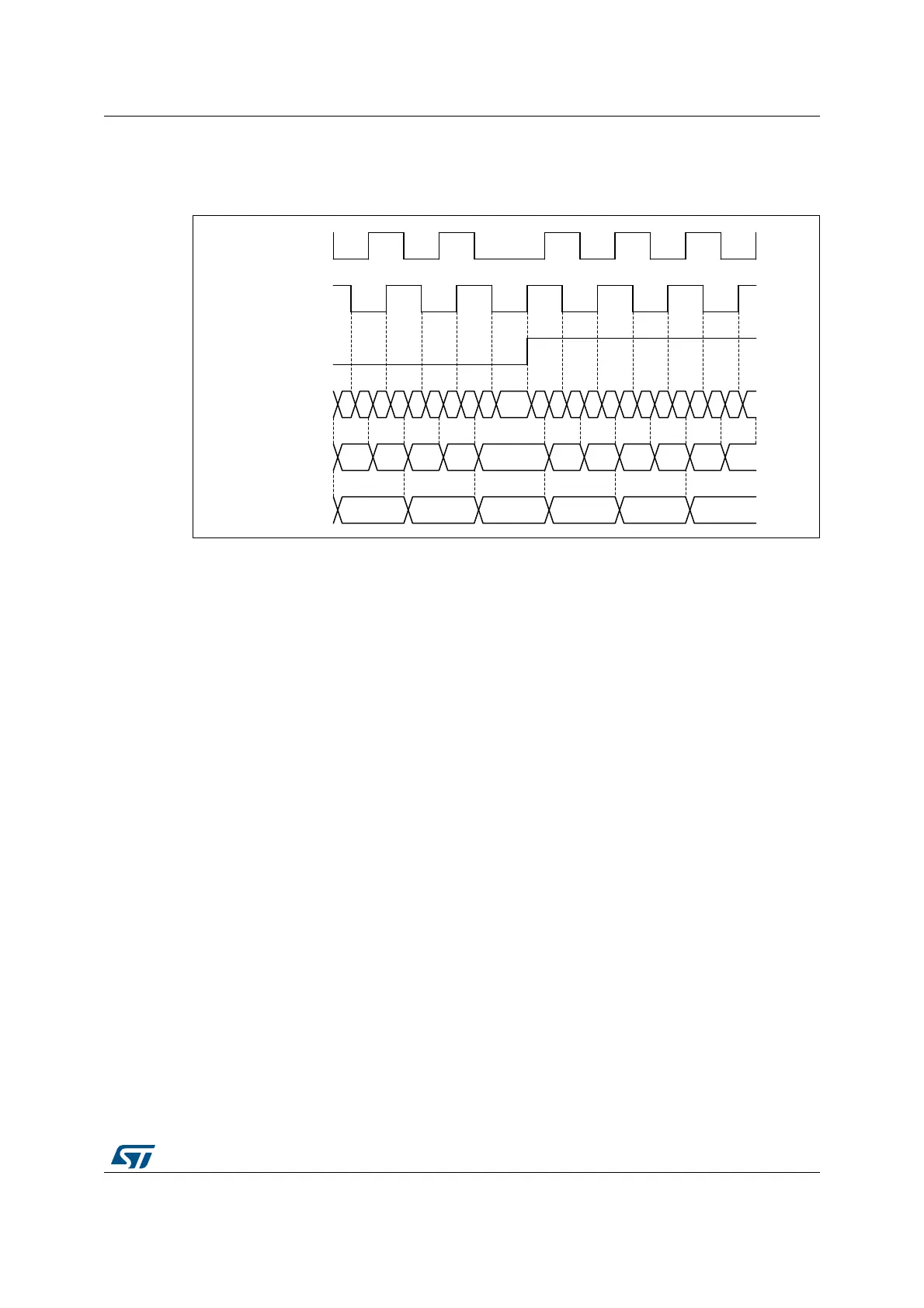

The Figure 407 below shows the timer counter value during a speed reversal, for various

counting modes.

Figure 407. Quadrature encoder counting modes

The timer, when configured in Encoder Interface mode provides information on the sensor’s

current position. Dynamic information can be obtained (speed, acceleration, deceleration)

by measuring the period between two encoder events using a second timer configured in

capture mode. The output of the encoder which indicates the mechanical zero can be used

for this purpose. Depending on the time between two events, the counter can also be read

at regular times. This can be done by latching the counter value into a third input capture

register if available (then the capture signal must be periodic and can be generated by

another timer). when available, it is also possible to read its value through a DMA request.

The IUFREMAP bit in the TIMx_CR1 register forces a continuous copy of the update

interrupt flag (UIF) into the timer counter register’s bit 31 (TIMxCNT[31]). This allows both

the counter value and a potential roll-over condition signaled by the UIFCPY flag to be read

in an atomic way. It eases the calculation of angular speed by avoiding race conditions

caused, for instance, by a processing shared between a background task (counter reading)

and an interrupt (update interrupt).

There is no latency between the UIF and UIFCPY flag assertions.

In 32-bit timer implementations, when the IUFREMAP bit is set, bit 31 of the counter is

overwritten by the UIFCPY flag upon read access (the counter’s most significant bit is only

accessible in write mode).

Clock plus direction encoder mode

In addition to the quadrature encoder mode, the timer offers support other types of

encoders.

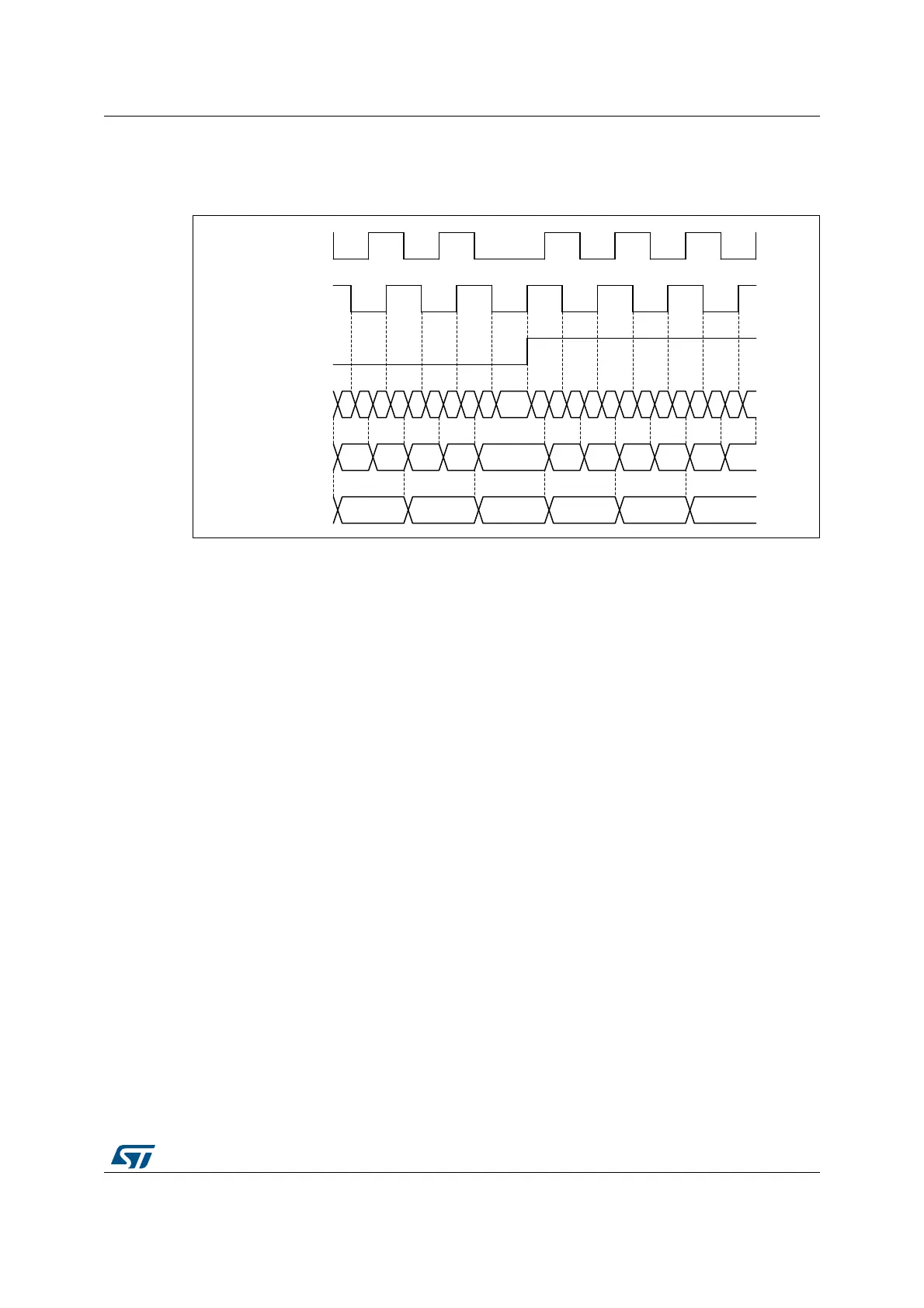

In the “clock plus direction” mode shown on Figure 408, the clock is provided on a single

line, on tim_ti2, while the direction is forced using the tim_ti1 input.

MSv62351V1

tim_ti2

DIR bit

Counter x2

Counter x4

Counter x1

9 0 1 0 9

8

6 7 8 9 0 1 2 3 4 5 4 3 2 1 0 9 8 7 6 5 4 3 2

8 0 1 2 1 0 9 8 7 69

tim_ti1

Loading...

Loading...