RM0440 Rev 4 1431/2126

RM0440 General-purpose timers (TIM15/TIM16/TIM17)

1445

Note: The state of the external I/O pins connected to the complementary tim_oc1 and tim_oc1n

channels depends on the tim_oc1 and tim_oc1n channel state and AFIO registers.

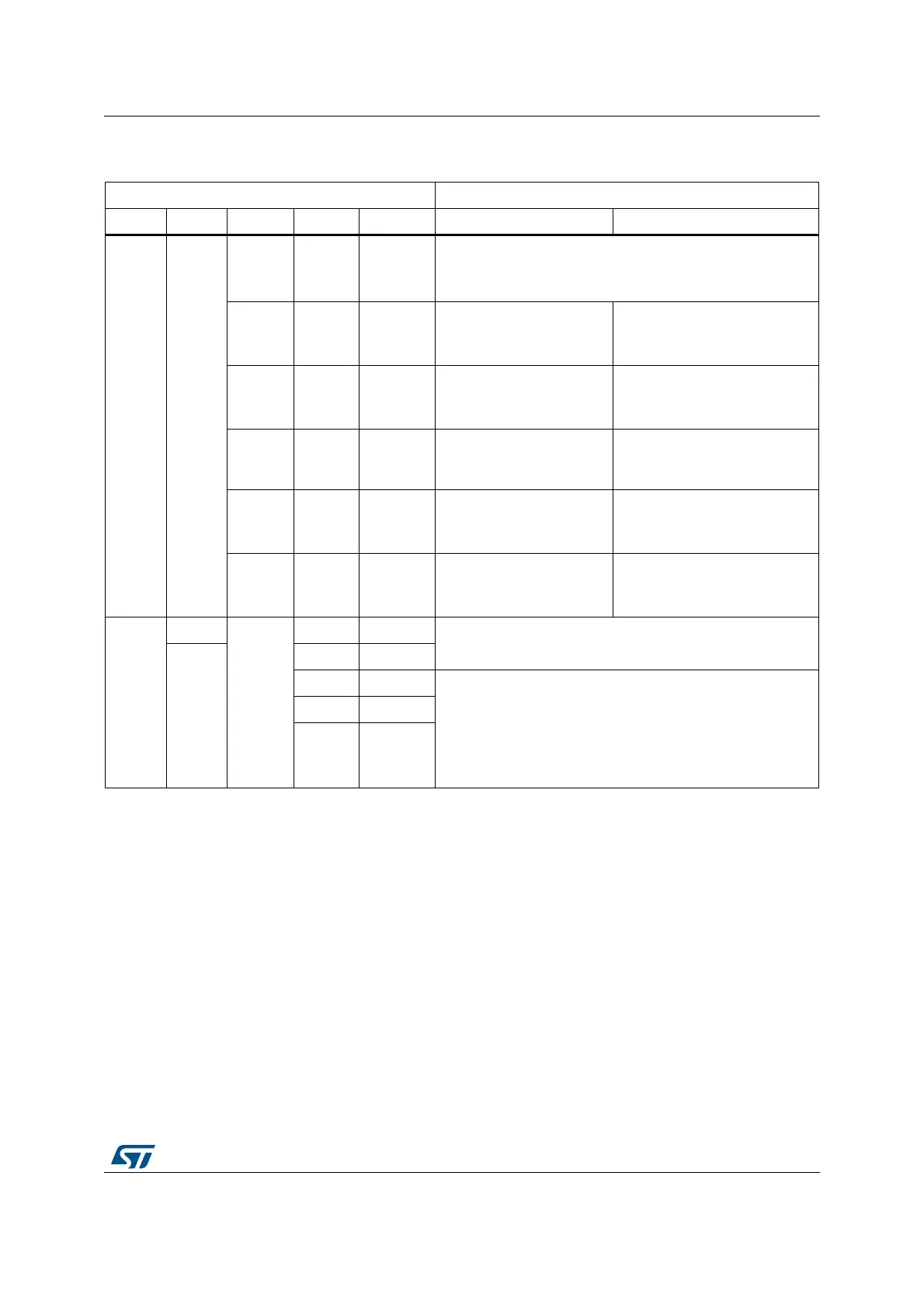

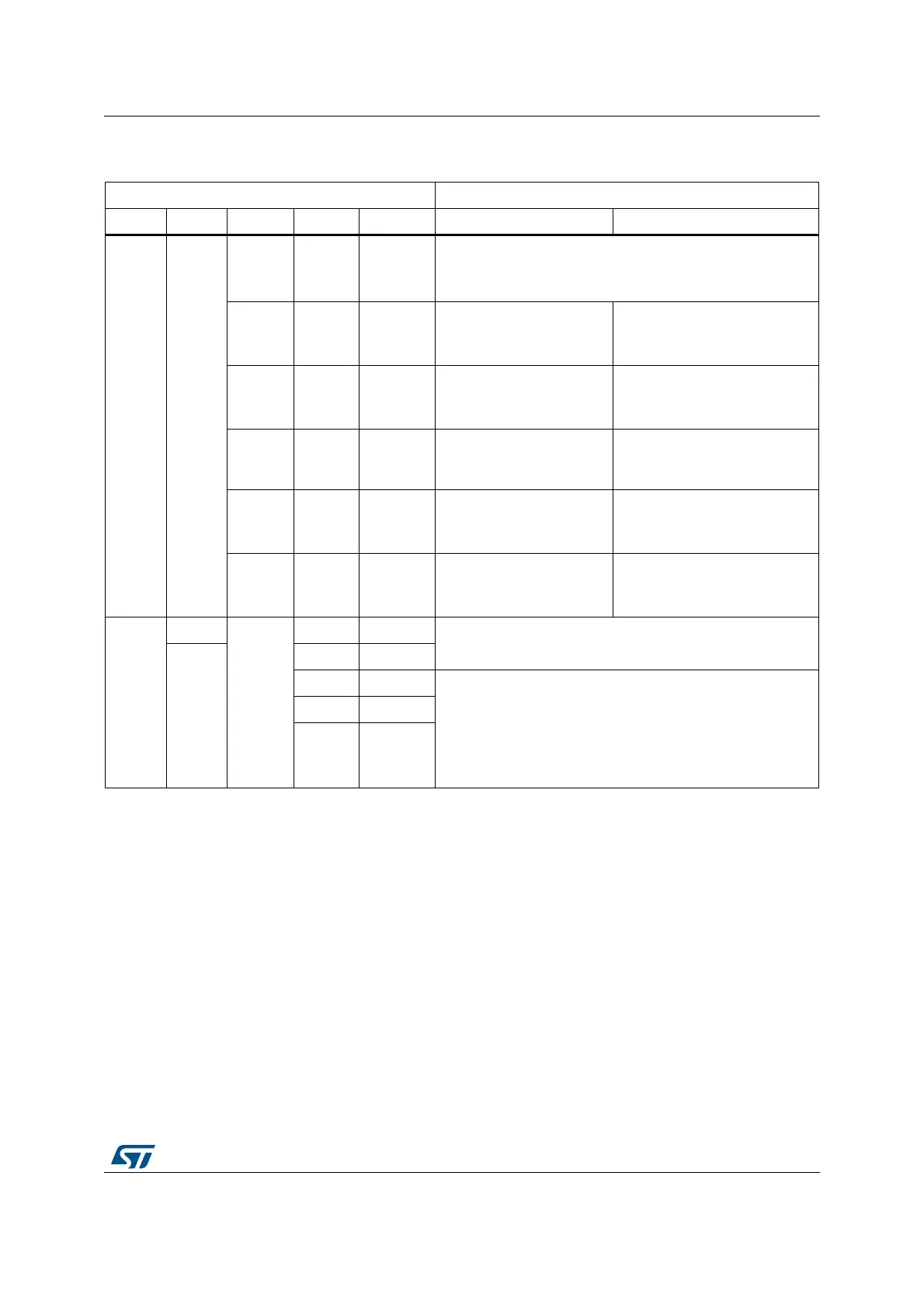

Table 301. Output control bits for complementary tim_oc1 and tim_oc1n channels with break

feature (TIM16/TIM17)

Control bits Output states

(1)

MOE bit OSSI bit OSSR bit CC1E bit CC1NE bit tim_oc1 output state tim_oc1n output state

1X

X0 0

Output Disabled (not driven by the timer: Hi-Z)

tim_oc1=0

tim_oc1n=0

00 1

Output Disabled (not driven

by the timer: Hi-Z)

tim_oc1=0

tim_oc1ref + Polarity

tim_oc1n=tim_oc1ref XOR

CC1NP

01 0

tim_oc1ref + Polarity

tim_oc1=tim_oc1ref XOR

CC1P

Output Disabled (not driven by

the timer: Hi-Z)

tim_oc1n=0

X1 1

tim_oc1ref + Polarity +

dead-time

Complementary to tim_oc1ref

(not tim_oc1ref) + Polarity +

dead-time

10 1

Off-State (output enabled

with inactive state)

tim_oc1=CC1P

tim_oc1ref + Polarity

tim_oc1n=tim_oc1ref XOR

CC1NP

11 0

tim_oc1ref + Polarity

tim_oc1=tim_oc1ref XOR

CC1P

Off-State (output enabled with

inactive state)

tim_oc1n=CC1NP

0

0

X

XX

Output disabled (not driven by the timer: Hi-Z)

1

00

0 1 Off-State (output enabled with inactive state)

Asynchronously: tim_oc1=CC1P, tim_oc1n=CC1NP

Then if the clock is present: tim_oc1=OIS1 and

tim_oc1n=OIS1N after a dead-time, assuming that OIS1 and

OIS1N do not correspond to tim_oc1 and tim_oc1n both in

active state

10

11

1. When both outputs of a channel are not used (control taken over by GPIO controller), the OIS1, OIS1N, CC1P and CC1NP

bits must be kept cleared.

Loading...

Loading...