RM0440 Rev 4 1253/2126

RM0440 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

1343

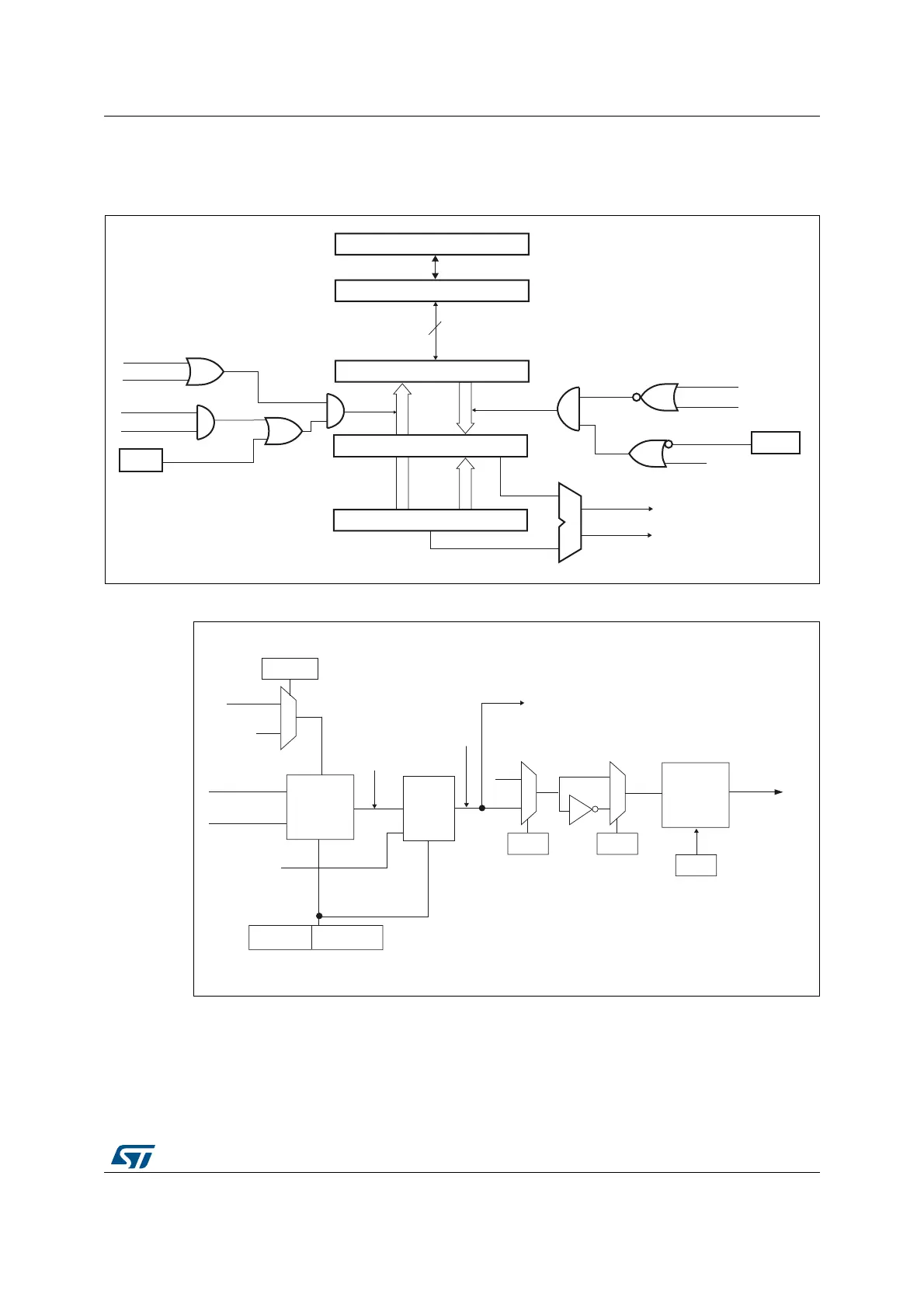

The output stage generates an intermediate waveform which is then used for reference:

tim_ocxref (active high). The polarity acts at the end of the chain.

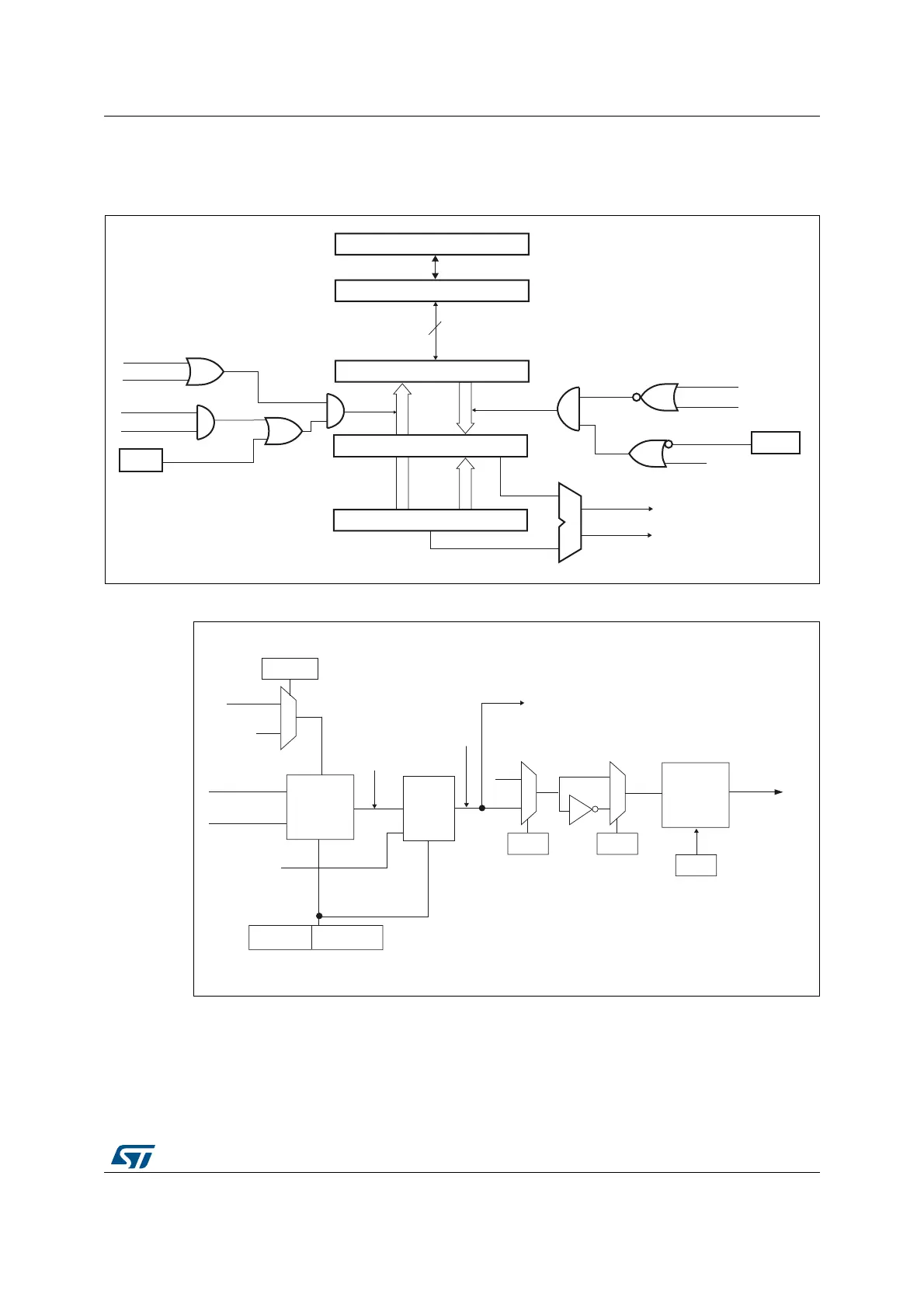

Figure 384. Capture/compare channel 1 main circuit

Figure 385. Output stage of capture/compare channel (channel 1, idem ch.2, 3 and 4)

1. Available on some instances only. If not available, tim_etrf is directly connected to tim_ocref_clr_int.

The capture/compare block is made of one preload register and one shadow register. Write

and read always access the preload register.

In capture mode, captures are actually done in the shadow register, which is copied into the

preload register.

MSv63030V1

CC1E

compare shadow register

Comparator

Capture/compare preload register

Counter

IC1PS

CC1S[0]

CC1S[1]

Capture

Input mode

CC1S[0]

CC1S[1]

Output mode

UEV

OC1PE

(from time

base unit)

Compare

transfer

APB Bus

16/32-bit

MCU-peripheral interface

TIMx_CCMR1

OC1PE

CNT>CCR1

CNT=CCR1

TIMx_EGR

CC1G

MSv62374V2

Output

mode

controller

CNT > CCR1

CNT = CCR1

TIMx_CCMR1

OC1M[3:0]

0

1

CC1P

TIMx_CCER

Output

enable

circuit

tim_oc1

CC1E

TIMx_CCER

To the master

mode controller

tim_oc1ref

OC1CE

0

1

CC1E

TIMx_CCER

‘0’

0

1

tim_ocref_clr_int

tim_etrf

tim_ocref_clr

OCCS

(1)

TIMx_SMCR

Output

selector

tim_oc1refc

tim_oc2ref

Loading...

Loading...