RM0440 Rev 4 851/2126

RM0440 High-resolution timer (HRTIM)

1083

27.3.3 Clocks

The HRTIM must be supplied by the t

HRTIM

APB2 clock to offer a full resolution. The t

HRTIM

clock period is evenly divided into up to 32 intermediate steps using an edge positioning

logic. All clocks present in the HRTIM are derived from this reference clock.

Definition of terms

f

HRTIM

: main HRTIM clock (hrtim_ker_ck). All subsequent clocks are derived and

synchronous with this source.

f

HRCK

: high-resolution equivalent clock. Considering the f

HRTIM

clock period division

by 32, it is equivalent to a frequency of 170 x 32 = 5.44 GHz.

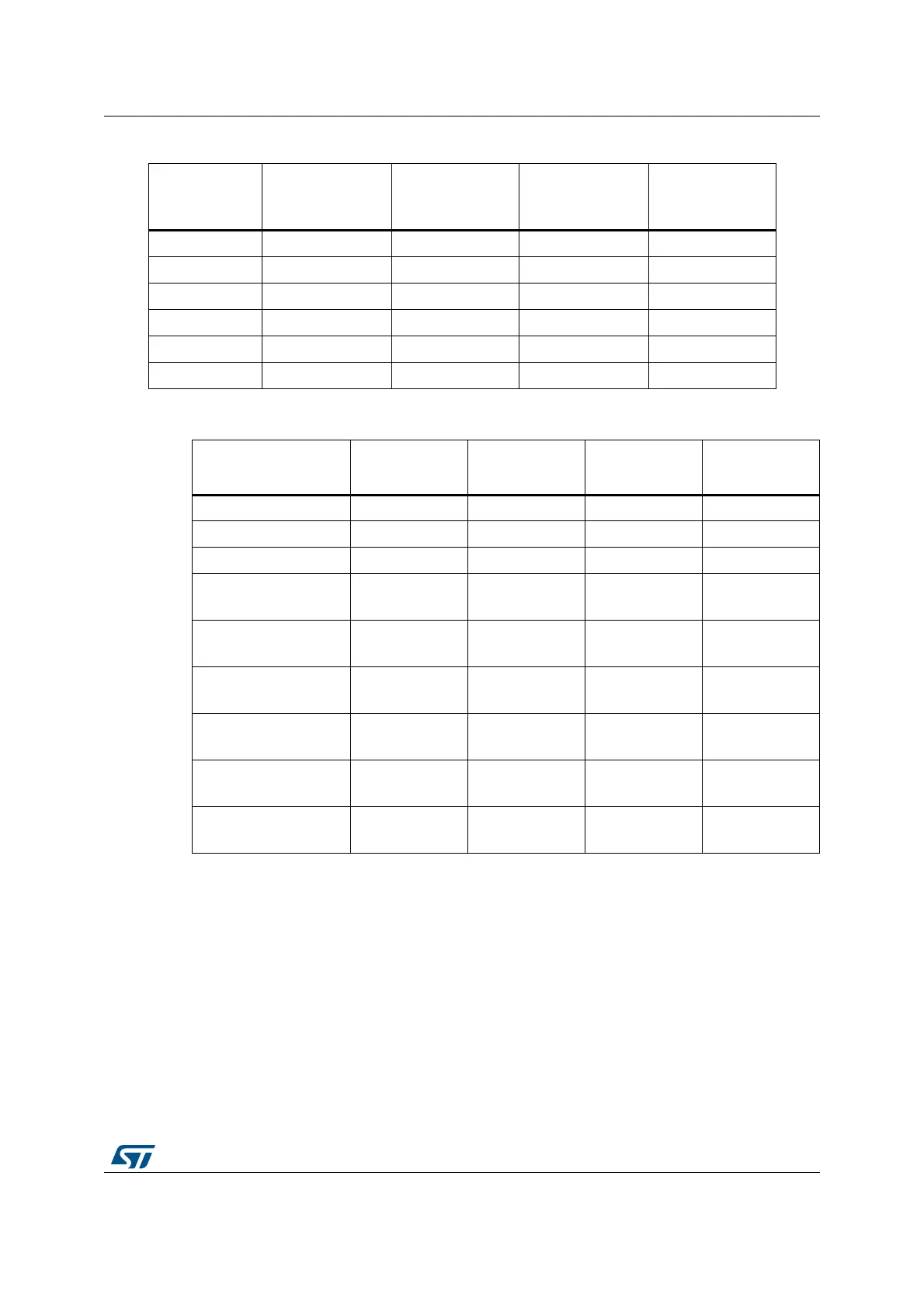

Table 211. Fault inputs

Fault channel

External Input

FLTxSRC[1:0] =

00

On-chip source

FLTxSRC[1:0] =

01

External Input

FLTxSRC[1:0] =

10

On-chip source

FLTxSRC[1:0] =

11

hrtim_in_flt1[4:1] PA12 COMP2 EEV1 N/A

hrtim_in_flt2[4:1] PA15 COMP4 EEV2 N/A

hrtim_in_flt3[4:1] PB10 COMP6 EEV3 N/A

hrtim_in_flt4[4:1] PB11 COMP1 EEV4 N/A

hrtim_in_flt5[4:1] PB0/PC7 COMP3 EEV5 N/A

hrtim_in_flt6[4:1] PC10 COMP5 EEV6 N/A

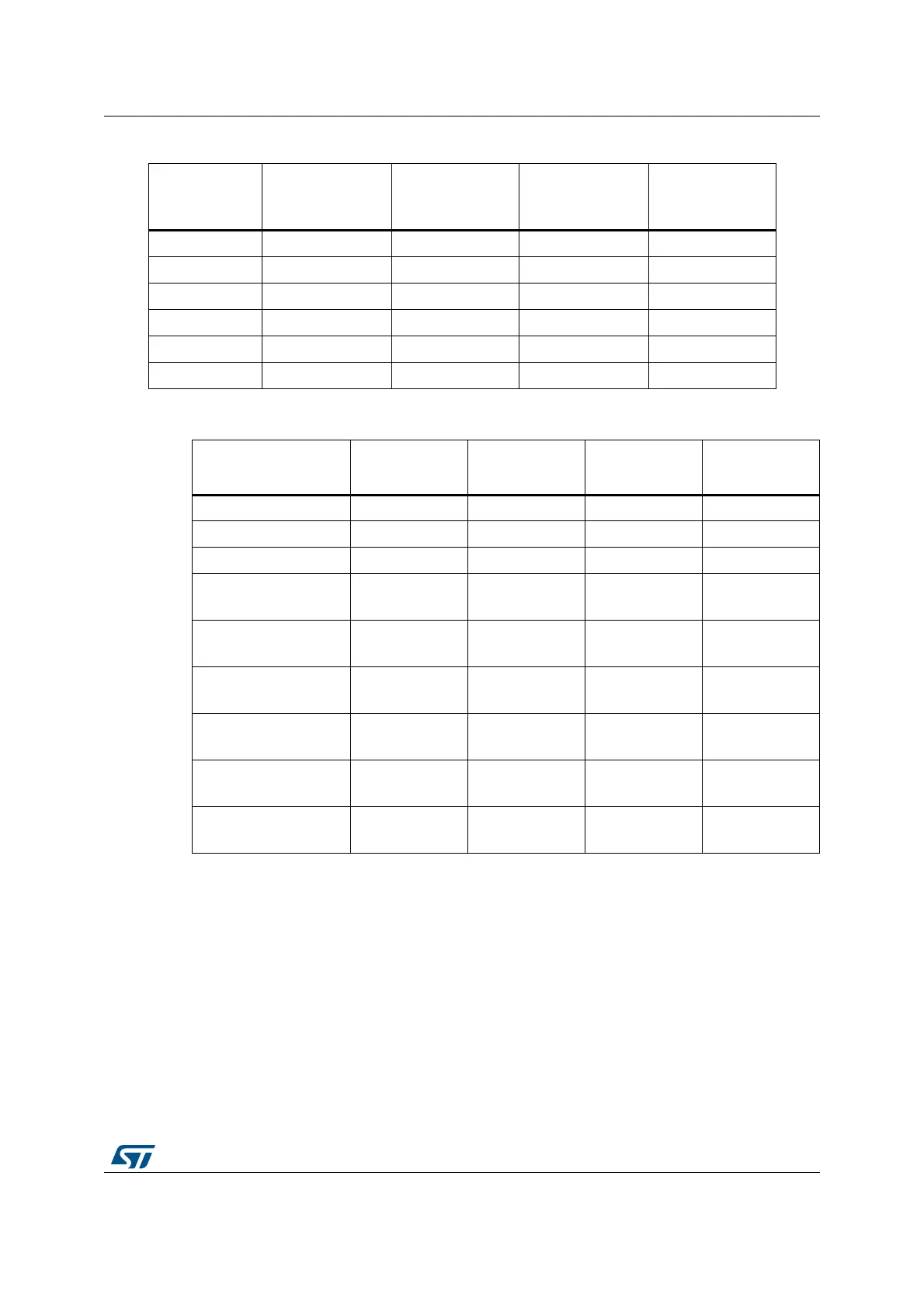

Table 212. HRTIM DAC triggers connections

HRTIM DAC triggers

DAC1_CH1

DAC_CH2

DAC2_CH1

DAC3_CH1

DAC3_CH2

DAC4_CH1

DAC4_CH2

hrtim_dac_trg1 Yes - - Yes

hrtim_dac_trig2 - Yes - -

hrtim_dac_trig3 - - Yes -

hrtim_dac_reset_trg1

hrtim_dac_step_trg1

Yes Yes Yes Yes

hrtim_dac_reset_trg2

hrtim_dac_step_trg2

Yes Yes Yes Yes

hrtim_dac_reset_trg3

hrtim_dac_step_trg3

Yes Yes Yes Yes

hrtim_dac_reset_trg4

hrtim_dac_step_trg4

Yes Yes Yes Yes

hrtim_dac_reset_trg5

hrtim_dac_step_trg5

Yes Yes Yes Yes

hrtim_dac_reset_trg6

hrtim_dac_step_trg6

Yes Yes Yes Yes

Loading...

Loading...