RM0440 Rev 4 531/2126

RM0440 Flexible static memory controller (FSMC)

571

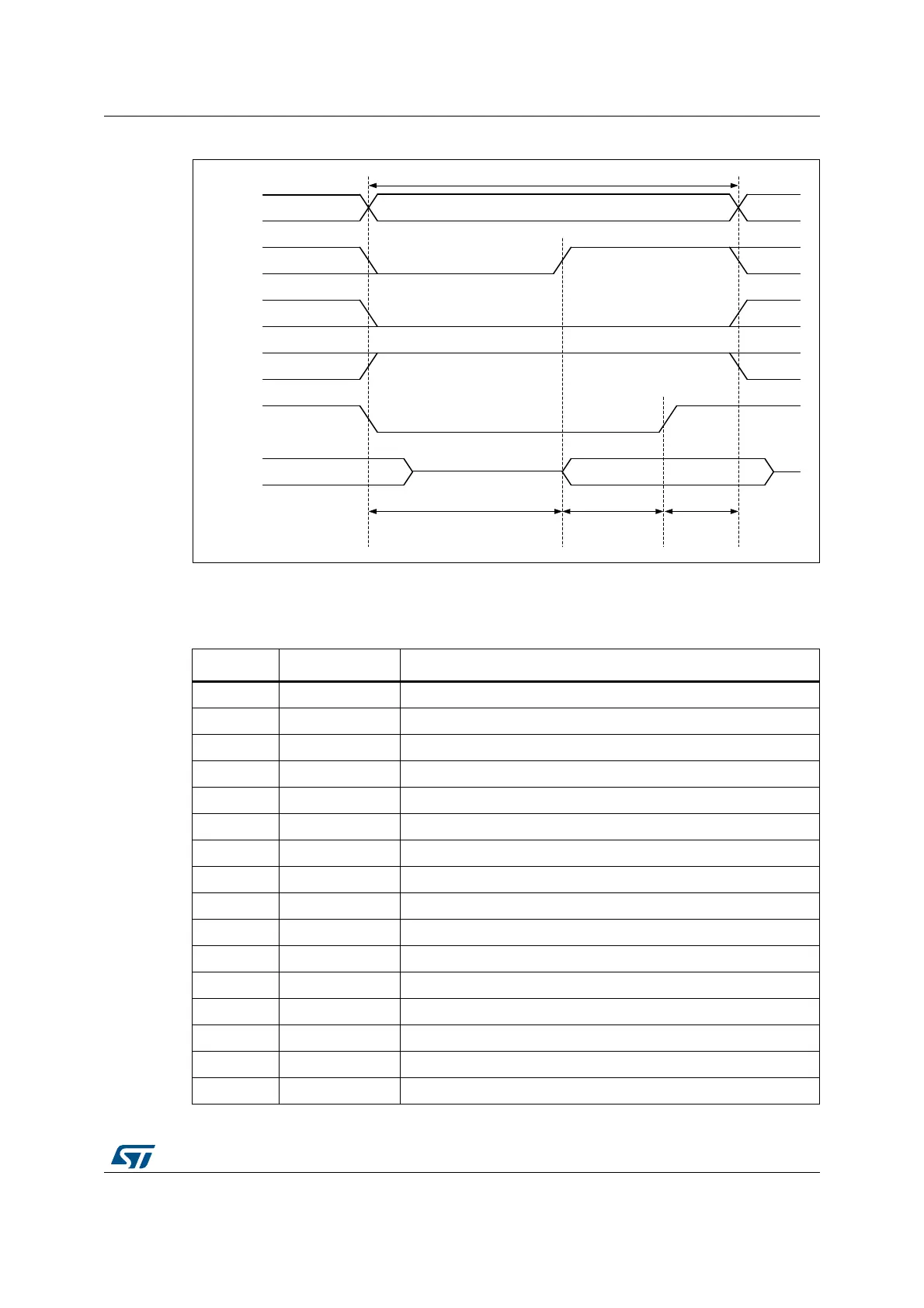

Figure 60. Mode B write access waveforms

The differences with mode 1 are the toggling of NWE and the independent read and write

timings when extended mode is set (mode B).

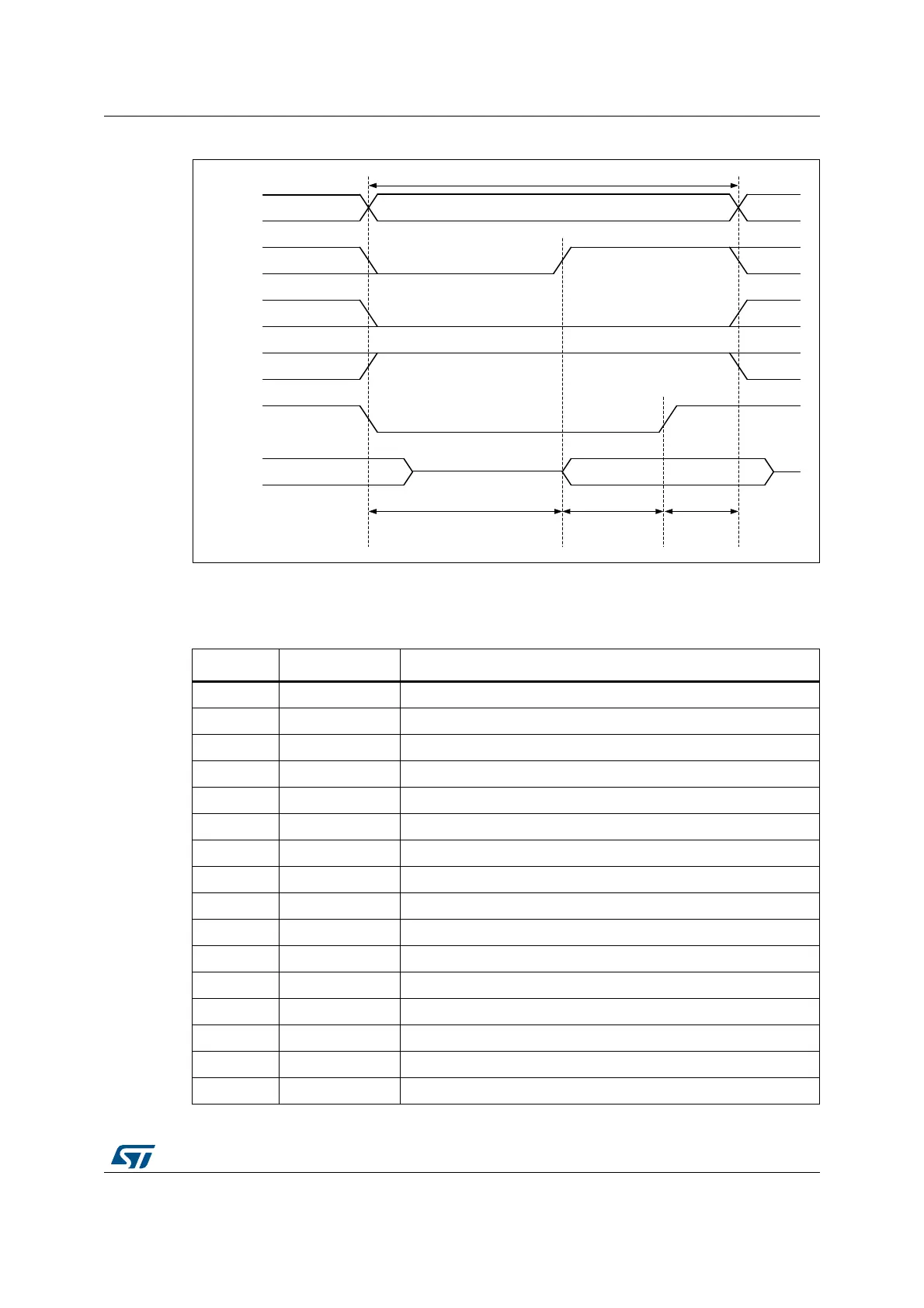

Table 134. FMC_BCRx bitfields (mode 2/B)

Bit number Bit name Value to set

31:24 Reserved 0x000

23:22 NBLSET[1:0] Don’t care

20 CCLKEN As needed

19 CBURSTRW 0x0 (no effect in Asynchronous mode)

18:16 CPSIZE 0x0 (no effect in Asynchronous mode)

15 ASYNCWAIT Set to 1 if the memory supports this feature. Otherwise keep at 0.

14 EXTMOD 0x1 for mode B, 0x0 for mode 2

13 WAITEN 0x0 (no effect in Asynchronous mode)

12 WREN As needed

11 WAITCFG Don’t care

10 Reserved 0x0

9 WAITPOL Meaningful only if bit 15 is 1

8 BURSTEN 0x0

7 Reserved 0x1

6 FACCEN 0x1

5:4 MWID As needed

MSv41680V1

A[25:0]

Memory transaction

NADV

NEx

NOE

Data driven by controller

NWE

Data bus

ADDSET HCLK cycles DATAST HCLK cycles DATAHLD +1

HCLK cycles

Loading...

Loading...