Embedded Flash memory (FLASH) for category 3 devices RM0440

132/2126 RM0440 Rev 4

3.7.6 Flash control register (FLASH_CR)

Address offset: 0x14

Reset value: 0xC000 0000

Access: no wait state when no Flash memory operation is on going, word, half-word and

byte access

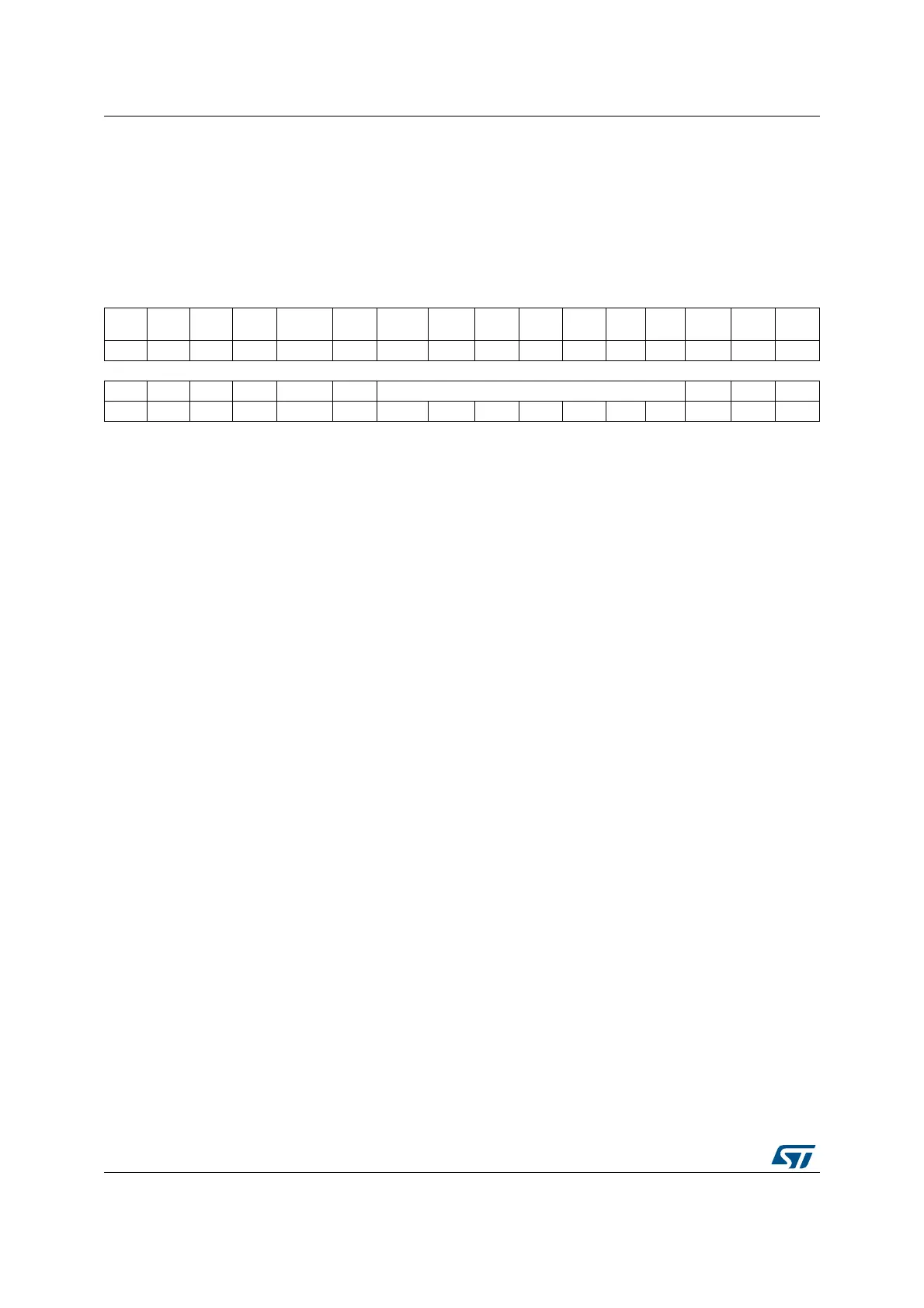

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LOCK

OPT

LOCK

SEC_

PROT2

SEC_

PROT1

OBL_

LAUNCH

RD

ERRIE

ERR

IE

EOP

IE

Res. Res. Res. Res. Res. FSTPG

OPT

STRT

STRT

rs rs rs rs rc_w1 rw rw rw rw rs rs

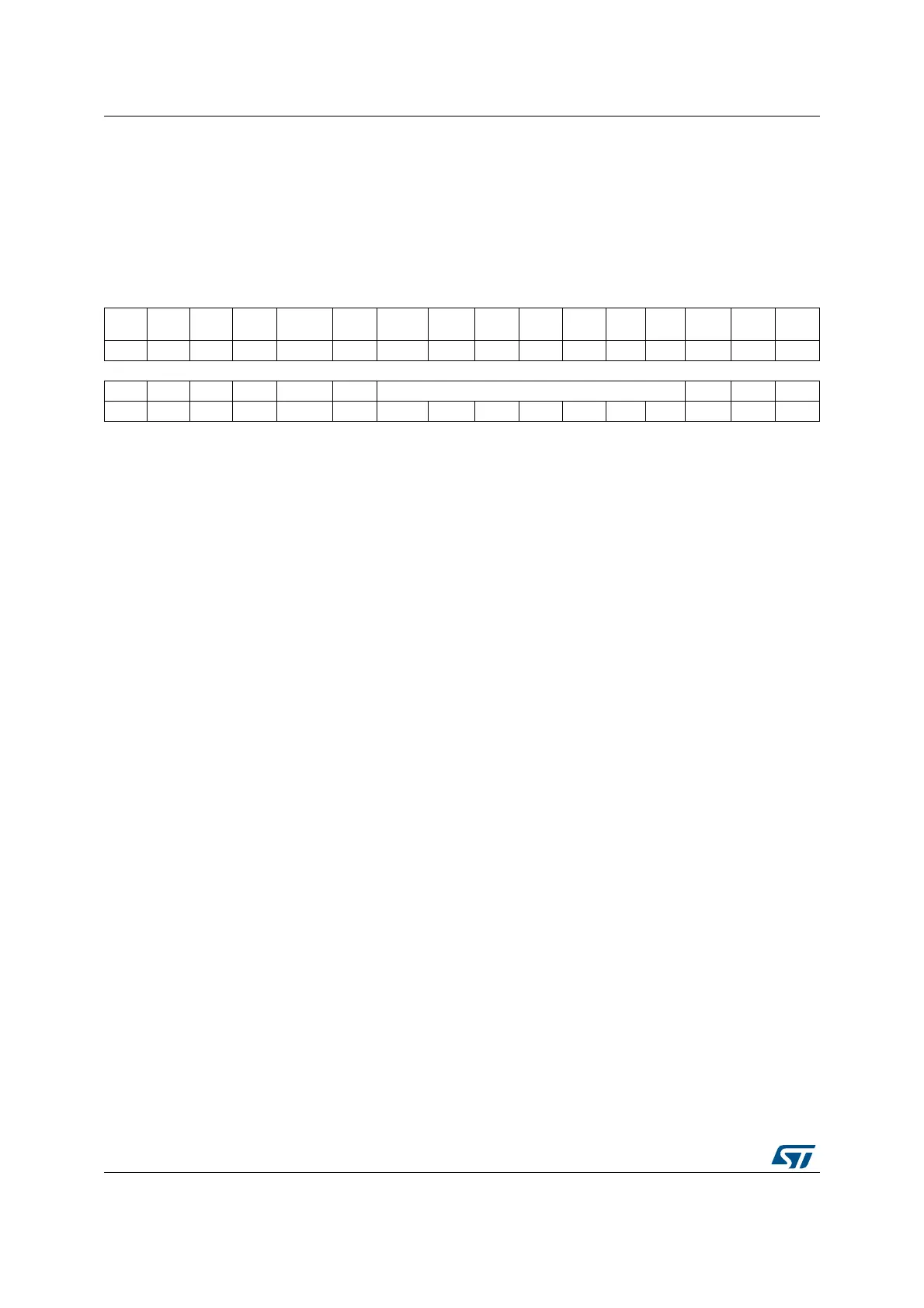

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MER2 Res. Res. Res. BKER Res. PNB[6:0] MER1 PER PG

rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 LOCK: FLASH_CR Lock

This bit is set only. When set, the FLASH_CR register is locked. It is cleared by

hardware after detecting the unlock sequence.

In case of an unsuccessful unlock operation, this bit remains set until the next

system reset.

Bit 30 OPTLOCK: Options Lock

This bit is set only. When set, all bits concerning user option in FLASH_CR

register and so option page are locked. This bit is cleared by hardware after

detecting the unlock sequence. The LOCK bit must be cleared before doing the

unlock sequence for OPTLOCK bit.

In case of an unsuccessful unlock operation, this bit remains set until the next

reset.

Bit 29 SEC_PROT2: Securable memory area protection bit for bank 2.

This bit is set to lock the access to the Securable area in bank 2. It is set by

software when exiting the Securable area, and can only be written once. In case

DBANK=0, this bit is useless.

Bit 28 SEC_PROT1: Securable memory area protection bit for bank 1.

This bit is set to lock the access to the Securable memory area for bank 1 (or when

DBANK=0). It is set by software when exiting the Securable area, and can only be

written once.

Bit 27 OBL_LAUNCH: Force the option byte loading

When set to 1, this bit forces the option byte reloading. This bit is cleared only

when the option byte loading is complete. It cannot be written if OPTLOCK is set.

0: Option byte loading complete

1: Option byte loading requested

Bit 26 RDERRIE: PCROP read error interrupt enable

This bit enables the interrupt generation when the RDERR bit in the FLASH_SR

is set to 1.

0: PCROP read error interrupt disabled

1: PCROP read error interrupt enabled

Loading...

Loading...