RM0440 Rev 4 1739/2126

RM0440 Serial peripheral interface / integrated interchip sound (SPI/I2S)

1791

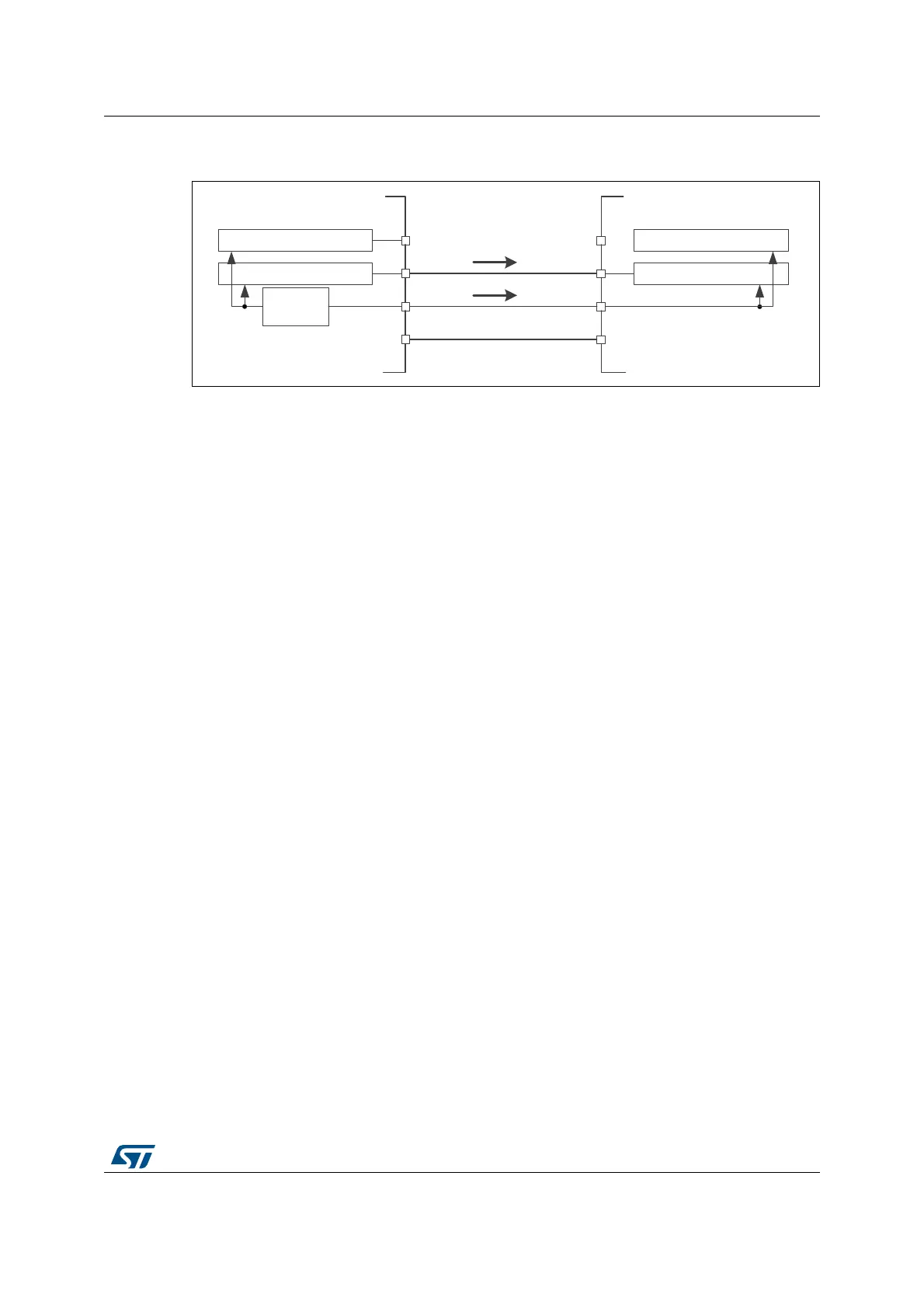

Figure 574. Simplex single master/single slave application (master in transmit-only/

slave in receive-only mode)

1. The NSS pins can be used to provide a hardware control flow between master and slave. Optionally, the

pins can be left unused by the peripheral. Then the flow has to be handled internally for both master and

slave. For more details see Section 39.5.5: Slave select (NSS) pin management.

2. An accidental input information is captured at the input of transmitter Rx shift register. All the events

associated with the transmitter receive flow must be ignored in standard transmit only mode (e.g. OVF

flag).

3. In this configuration, both the MISO pins can be used as GPIOs.

Note: Any simplex communication can be alternatively replaced by a variant of the half-duplex

communication with a constant setting of the transaction direction (bidirectional mode is

enabled while BDIO bit is not changed).

39.5.3 Standard multi-slave communication

In a configuration with two or more independent slaves, the master uses GPIO pins to

manage the chip select lines for each slave (see Figure 575.). The master must select one

of the slaves individually by pulling low the GPIO connected to the slave NSS input. When

this is done, a standard master and dedicated slave communication is established.

Rx shift register

Tx shift register Rx shift register

Tx shift register

SPI clock

generator

Master

Slave

MISO

MOSI

SCK

NSS

MISO

MOSI

SCK

NSS

(1) (1)

(2)

MSv39625V1

Loading...

Loading...