RM0440 Rev 4 1605/2126

RM0440 Universal synchronous/asynchronous receiver transmitter (USART/UART)

1733

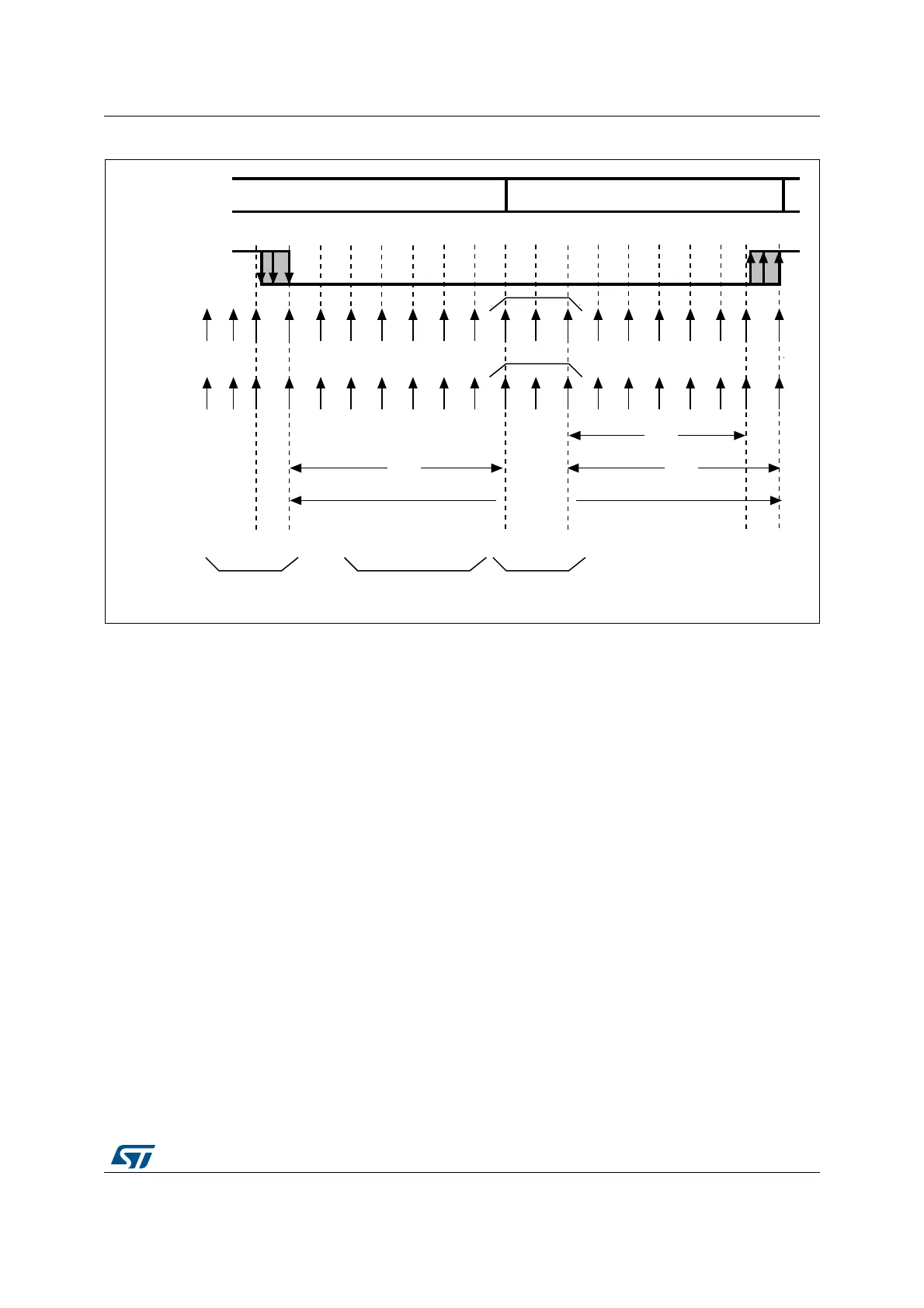

Figure 534. Start bit detection when oversampling by 16 or 8

Note: If the sequence is not complete, the start bit detection aborts and the receiver returns to the

idle state (no flag is set), where it waits for a falling edge.

The start bit is confirmed (RXNE flag set and interrupt generated if RXNEIE=1, or RXFNE

flag set and interrupt generated if RXFNEIE=1 if FIFO mode enabled) if the 3 sampled bits

are at ‘0’ (first sampling on the 3rd, 5th and 7th bits finds the 3 bits at ‘0’ and second

sampling on the 8th, 9th and 10th bits also finds the 3 bits at ‘0’).

The start bit is validated but the NE noise flag is set if,

a) for both samplings, 2 out of the 3 sampled bits are at ‘0’ (sampling on the 3rd, 5th

and 7th bits and sampling on the 8th, 9th and 10th bits)

or

b) for one of the samplings (sampling on the 3rd, 5th and 7th bits or sampling on the

8th, 9th and 10th bits), 2 out of the 3 bits are found at ‘0’.

If neither of the above conditions are met, the start detection aborts and the receiver returns

to the idle state (no flag is set).

01 0 X0 X 000 0 X XXXXX

Falling edge

detection

11

1 2 3 4 5 6 7 8 9 10 111213141516

X X X X X X X X 9 10 111213141516

6/16

7/167/16

X

At least 2 bits

out of 3 at 0

At least 2 bits

out of 3 at 0

One-bit time

Conditions

to validate

the start bit

Real

sample

clock

Ideal

sample

clock

RX line

RX state

Idle

Start bit

Sampled values

ai15471b

Loading...

Loading...