RM0440 Rev 4 943/2126

RM0440 High-resolution timer (HRTIM)

1083

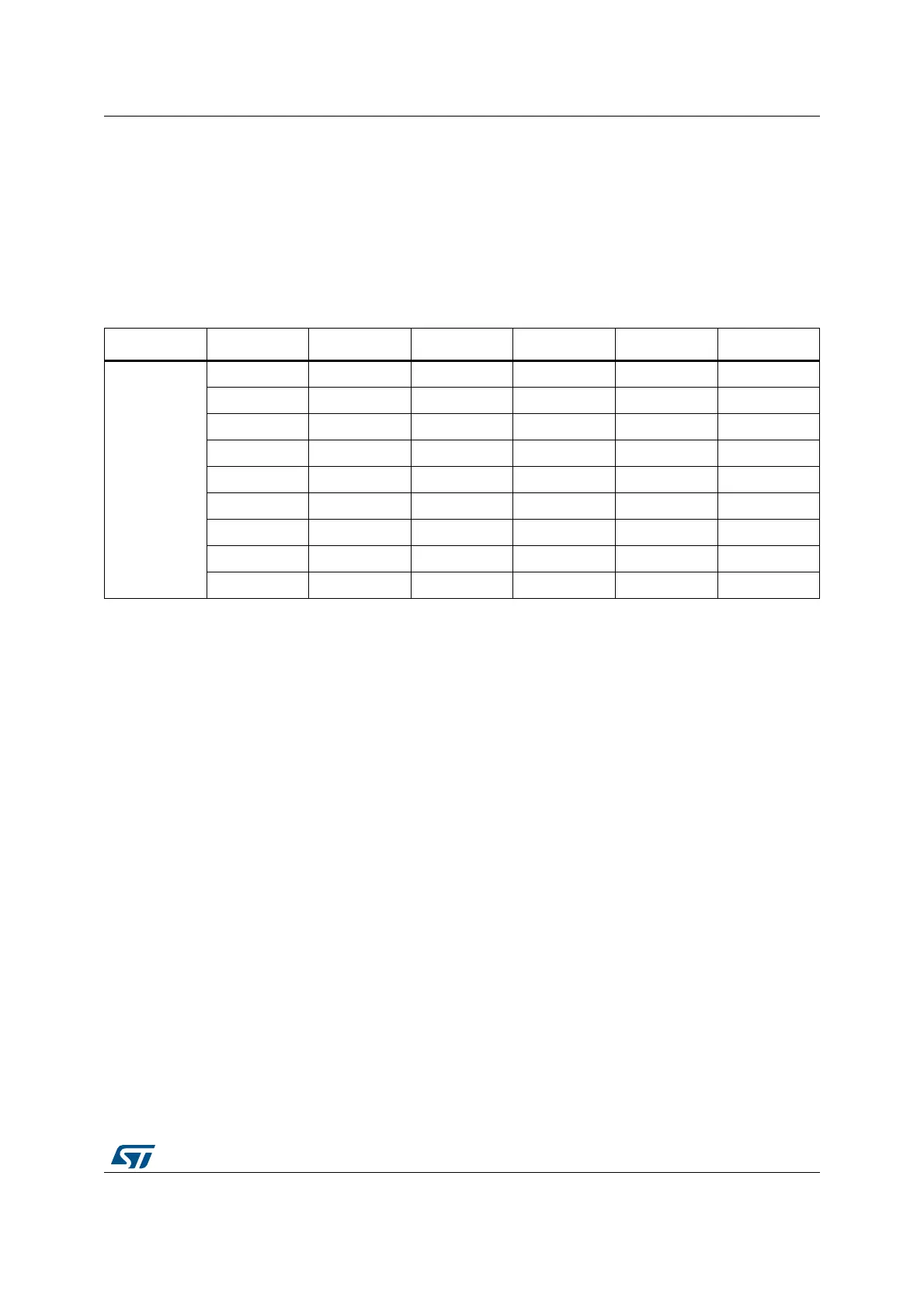

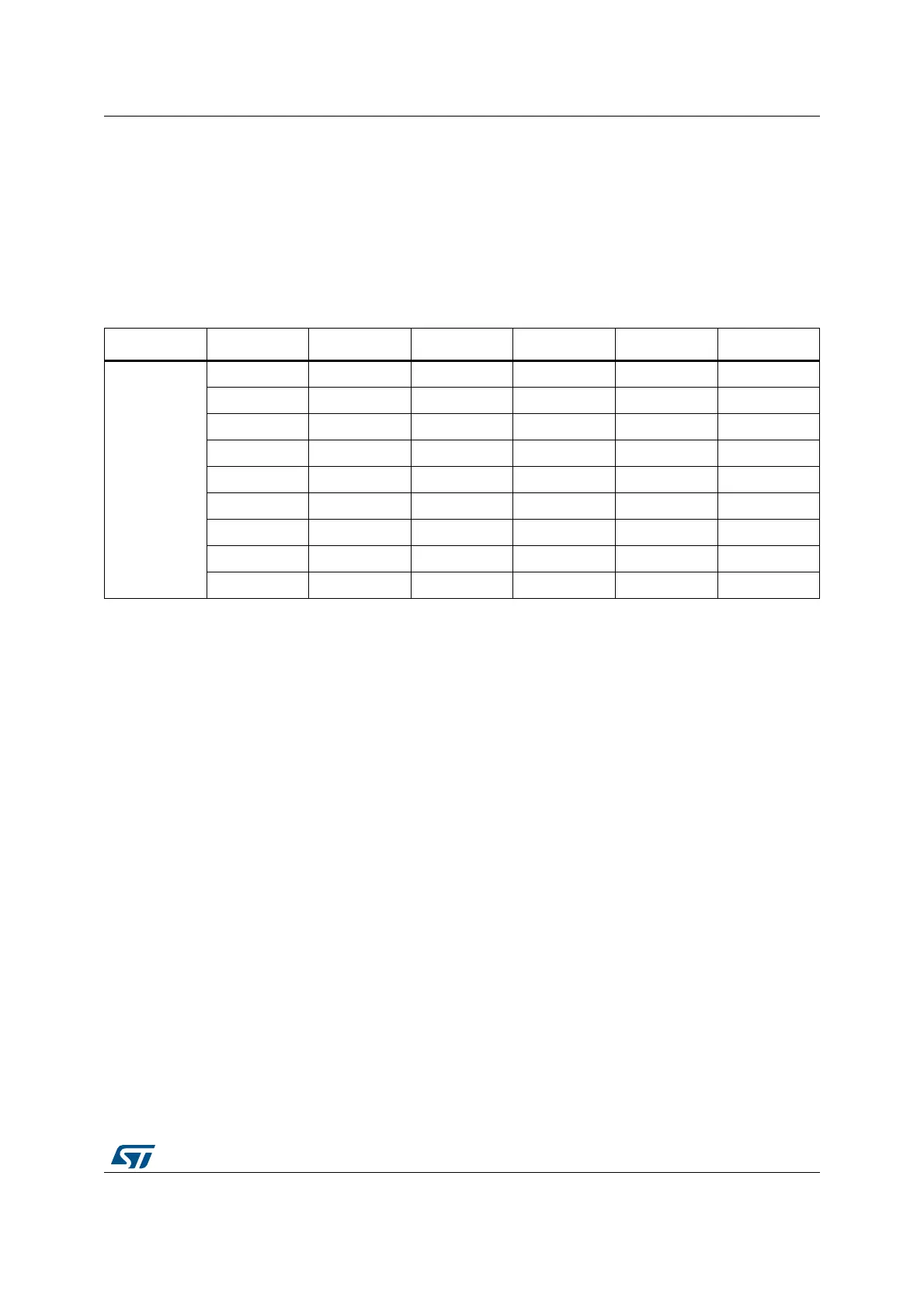

Table 238 below gives an example, for generating 6 triggers within a PWM period. It shows

that it is necessary to round up the division result to the upper value.

Let’s consider a counter period TIMxPER = 8192. Dividing 8192 by 6 yields 1365.33.

– Round down value: 1365: 7 triggers are generated, the 6th and 7th being very

close (respectively for counter = 8190 and 8192)

– Round up value:1366: 6 triggers are generated. The 6th trigger on dac_step_trg

(for counter = 8192) is aborted by the counter roll-over from 8192 to 0.

Note: In centered-pattern mode, it is mandatory to have an even number of triggers per switching

period, so as to avoid unevenly spaced triggers around counter’s peak value.

Table 238. DAC dual channel trigger example

- CMP2 = 1365 dac_trg dac_step_trg CMP2 = 1366 dac_trg dac_step_trg

Counter value

1365 - 1 1366 - 1

2730 - 2 2732 - 2

4095 - 3 4098 - 3

5460 - 4 5464 - 4

6825 - 5 6830 - 5

8190 - 6 8192 6 -

8192 7 - 1366 - 1

1365 - 1 2732 - 2

... - - ... - -

Loading...

Loading...