RM0440 Rev 4 939/2126

RM0440 High-resolution timer (HRTIM)

1083

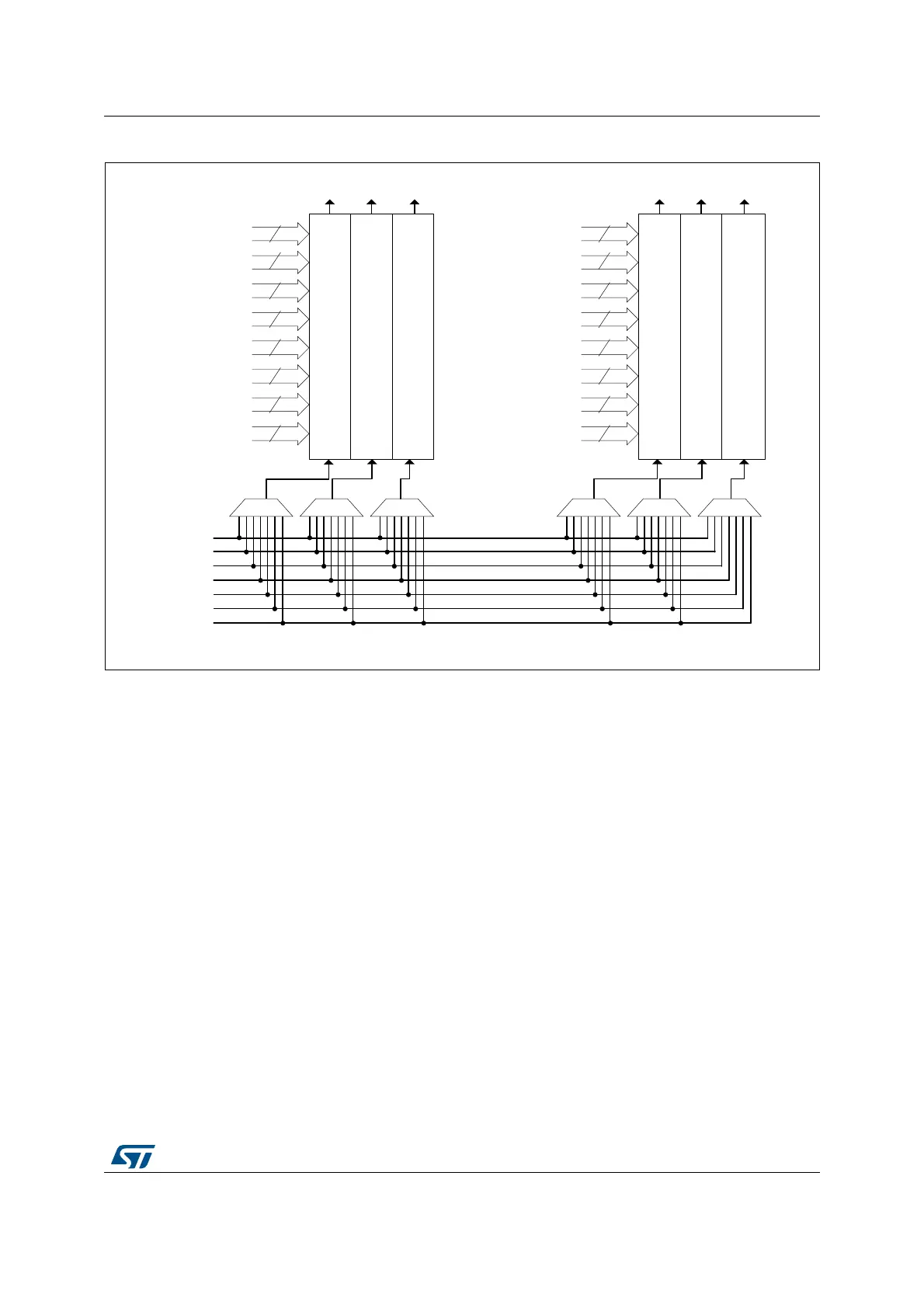

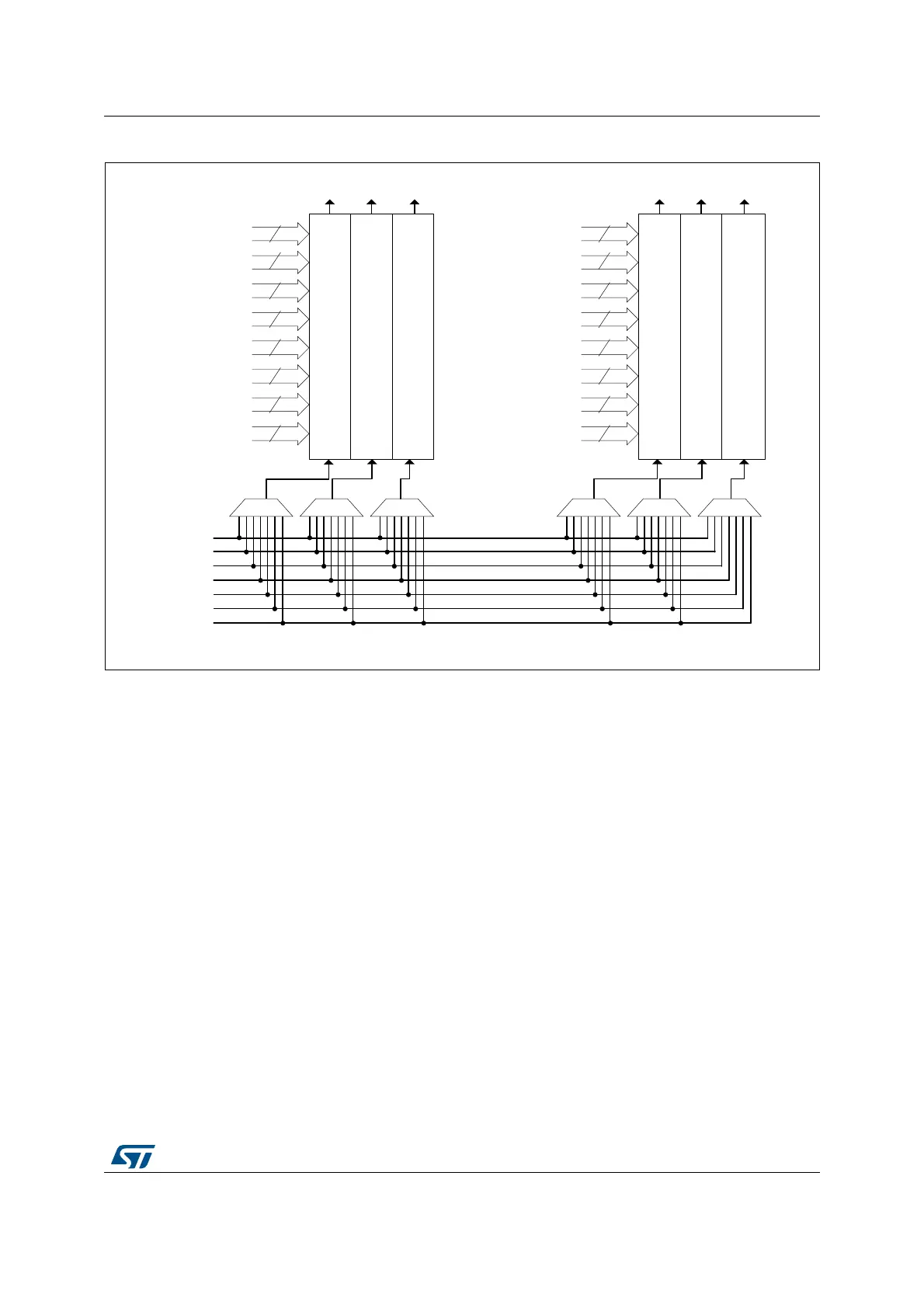

Figure 252. ADC triggers

HRTIM_ADC1R to HRTIM_ADC4R and HRTIM_ADCER registers are preloaded and can

be updated synchronously with the timer they are related to. The update sources are

defined with ADxUSRC[2:0] bits in the HRTIM_CR1 and HRTIM_ADCUR registers.

For instance, if ADC trigger 1 outputs timer A CMP2 events (HRTIM_ADC1R = 0x0000

0400), HRTIM_ADC1R is typically updated simultaneously with timer A (AD1USRC[2:0] =

001).

When the preload is disabled (PREEN bit reset) in the source timer, the HRTIM_ADCxR

registers are not preloaded either: a write access results in an immediate update of the

trigger source.

ADC post-scaler

A post-scaling unit allows to reduce the ADC trigger rate as shown in Figure 253 below.

Each ADC trigger rate can be individually adjusted using the ADCxPSC[4:0] bits in the

HRTIM_ADCxPS1 and HRTIM_ADCxPS2 registers.

In the center-aligned mode, the ADC trigger rate is also dependent on ADROM[1:0] bitfield,

programmed in the source timer, as shown in Figure 254. The ADROM[1:0] bitfield is coding

for any event that can trigger the ADC: reset, roll-over (period) and compare event:

• ADROM[1:0] = 00: event generated both during up and down-counting phases

• ADROM[1:0] = 01: event generated during down-counting phases

• ADROM[1:0] = 10: event generated during up-counting phases

MSv48357V2

Master Cmp1,2,3,4 + PER

TimerC Cmp3,4 + PER

TimerD Cmp3,4 + PER

TimerE Cmp3,4 + PER

External Events 1..5

5

5

5

5

4

4

4

Master Cmp1,2,3,4 + PER

TimerA Cmp2,4 + PER

TimerB Cmp2,4 + PER

TimerC Cmp2,4 + PER + RST

TimerD Cmp2,4 + PER + RST

TimerE Cmp2,3,4 + RST

External Events 6..10

5

5

4

4

5

5

4

Timer A update

Timer C update

Timer B update

Timer D update

Timer E update

Master update

TimerB Cmp3,4 + PER + RST

TimerA Cmp3,4 + PER + RST

Timer F update

4

TimerF Cmp2,3,4 + PER

4

Sources in bold are available only on Trigger 5,7,9 or trigger 6,8,10

ADC

Trigger 8

1 source

only

ADC

Trigger 6

1 Source

only

Trigger 6

Update

Trigger 8

Update

ADC

Trigger 10

1 Source

only

Trigger 10

Update

ADC

Trigger 7

1 source

only

ADC

Trigger 5

1 Source

only

Trigger 5

Update

Trigger 7

Update

ADC

Trigger 9

1 Source

only

Trigger 9

Update

AD6USRC AD8USRC AD10USRCAD5USRC AD7USRC AD9USRC

TimerF Cmp2,3,4 + PER + RST

hrtim_adc

_trg5

hrtim_adc

_trg7

hrtim_adc

_trg9

hrtim_adc

_trg6

hrtim_adc

_trg8

hrtim_adc

_trg10

Loading...

Loading...