RM0440 Rev 4 941/2126

RM0440 High-resolution timer (HRTIM)

1083

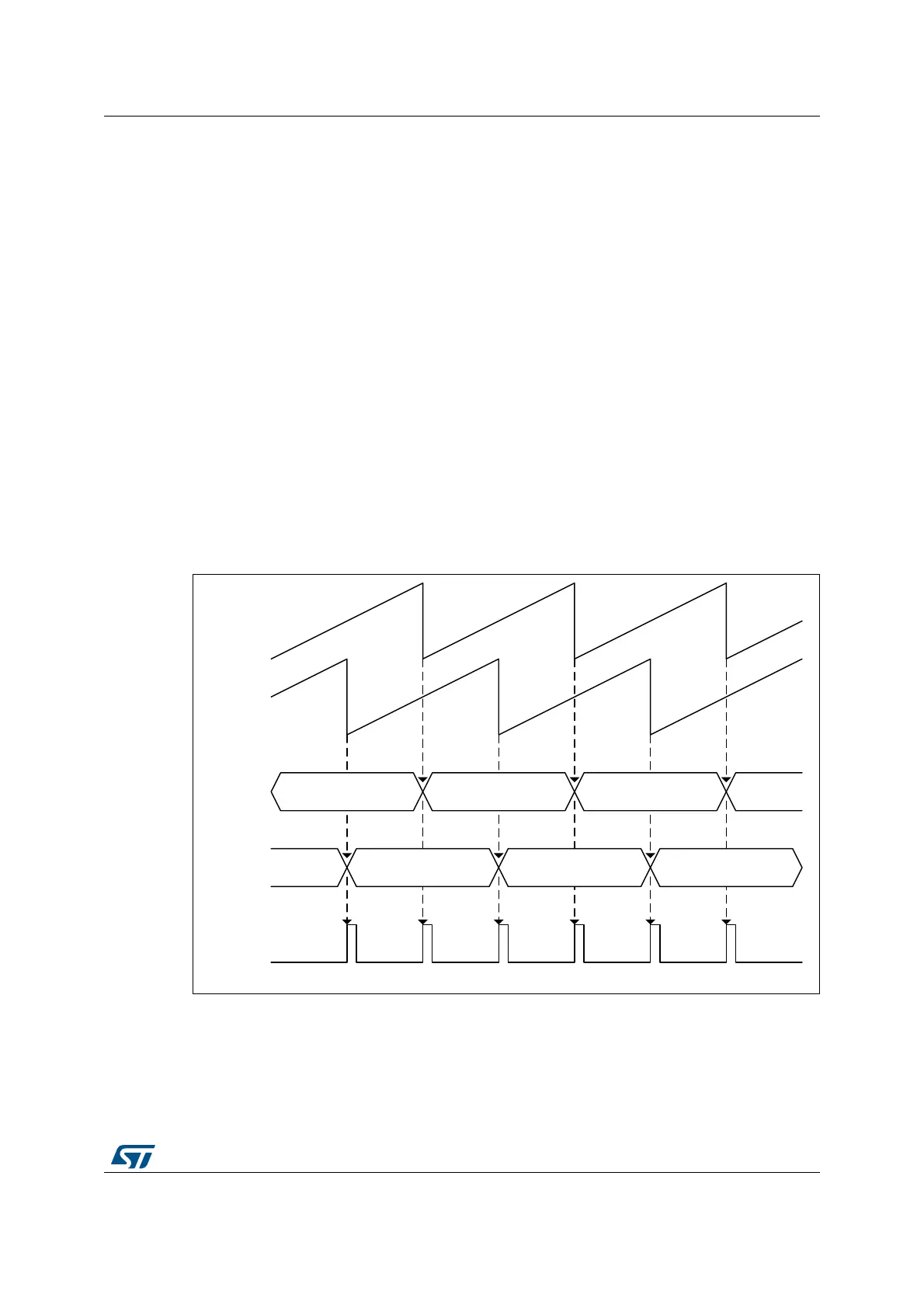

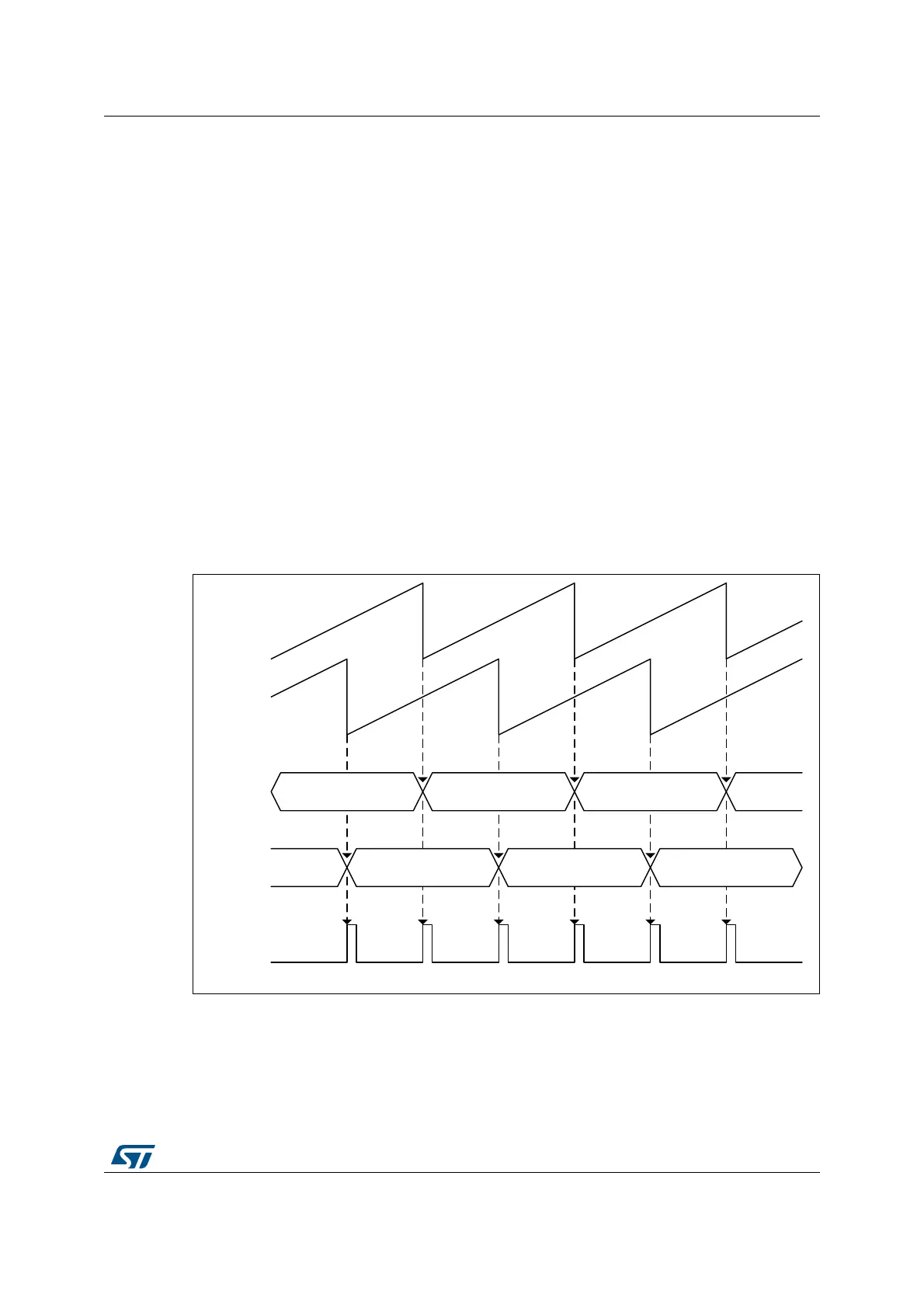

27.3.21 DAC triggers

The HRTIM allows to have the embedded DACs updated synchronously with the timer

updates.

The update events from the master timer and the timer units can generate DAC update

triggers on any of the 3 hrtim_dac_trgx outputs.

Note: Each timer has its own DAC-related control register.

DACSYNC[1:0] bits of the HRTIM_MCR and HRTIM_TIMxCR registers are programmed as

follows:

• 00: No update generated

• 01: Update generated on hrtim_dac_trg1

• 10: Update generated on hrtim_dac_trg2

• 11: Update generated on hrtim_dac_trg3

An output pulse of 1 f

HRTIM

clock periods is generated on the hrtim_dac_trgx output.

When DACSYNC[1:0] bits are enabled in multiple timers, the hrtim_dac_trgx output consists

of an OR of all timers’ update events. For instance, if DACSYNC = 1 in timer A and in timer

B, the update event in timer A is ORed with the update event in timer B to generate a DAC

update trigger on the corresponding hrtim_dac_trgx output, as shown on Figure 255.

Figure 255. Combining several updates on a single hrtim_dac_trgx output

Refer to Table 212: HRTIM DAC triggers connections for connections to the DACs.

MS32339V1

0x0000 1000 0x0000 1001 0x0000 1002

0x0000 1500 0x0000 1510 0x0000 1520

Timer A

counter

Timer B

counter

Timer A

Compare 2

register

DAC

TrigOutx

Timer B

Compare 4

register

TA update

TA update TA update

TB update TB update TB update

Loading...

Loading...