RM0440 Rev 4 889/2126

RM0440 High-resolution timer (HRTIM)

1083

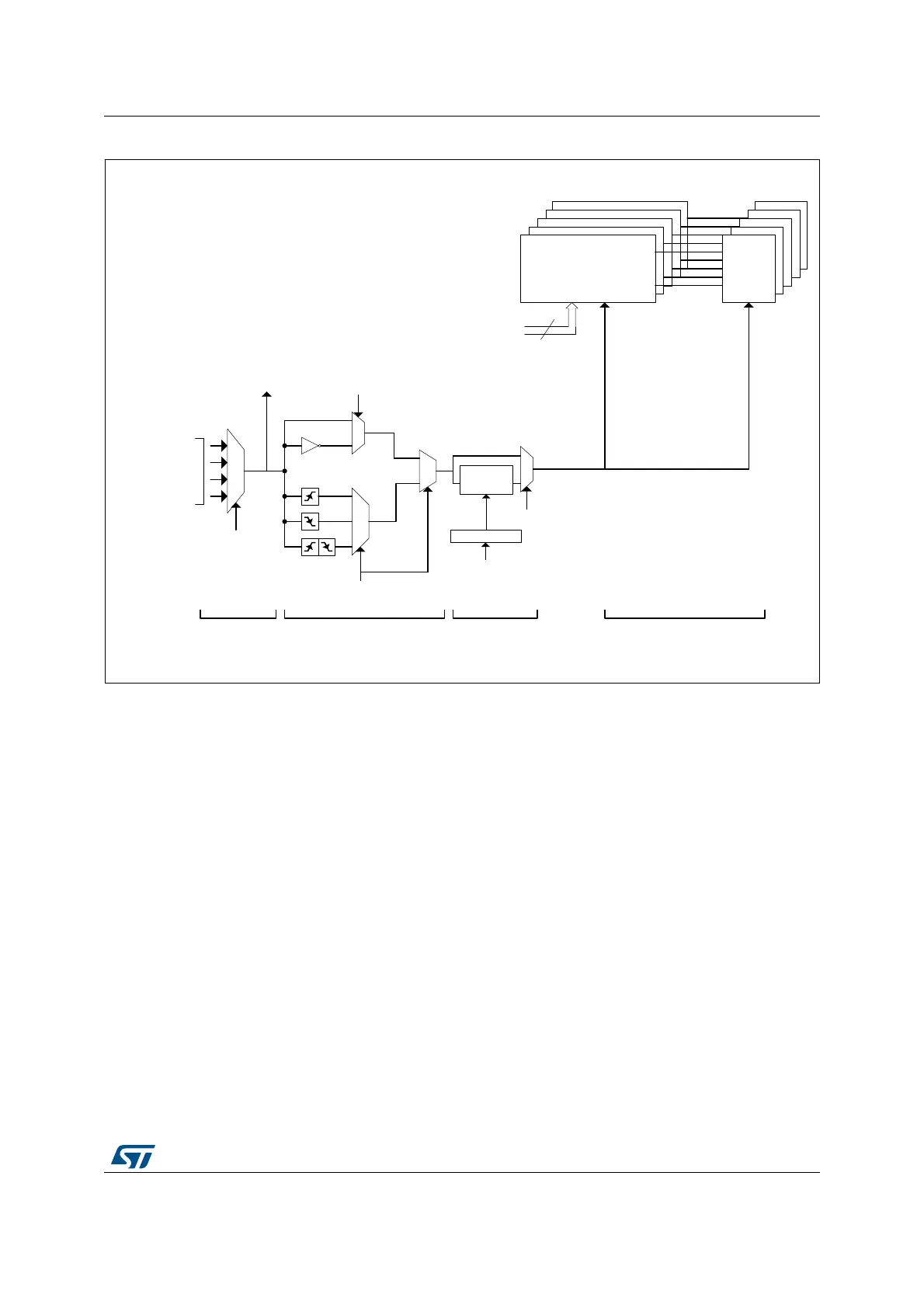

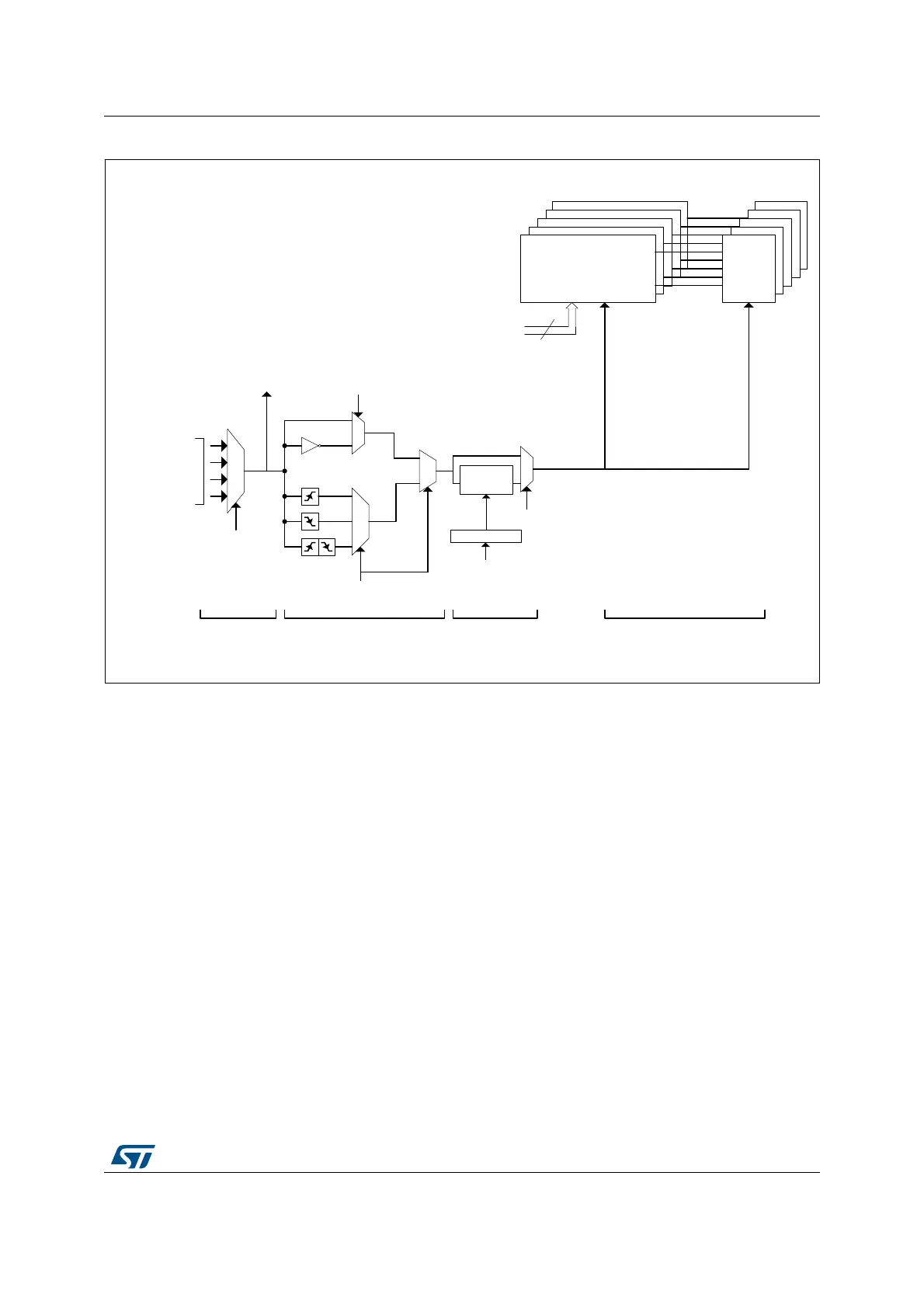

Figure 216. External event conditioning overview (1 channel represented)

The 10 external events are initialized using the HRTIM_EECR1 and HRTIM EECR2

registers:

• to select up to 4 sources with the EExSRC[1:0] bits,

• to select the sensitivity with EExSNS[1:0] bits, to be either level-sensitive or edge-

sensitive (rising, falling or both),

• to select the polarity, in case of a level sensitivity, with EExPOL bit,

• to have a low latency mode, with EExFAST bits (see Section : Latency to external

events), for external events 1 to 5.

Note: The external events used as triggers for reset, capture, burst mode, ADC triggers and

delayed protection are edge-sensitive even if EESNS bit is reset (level-sensitive selection):

if POL = 0 the trigger is active on external event rising edge, while if POL = 1 the trigger is

active on external event falling edge.

The external events are discarded as long as the counters are disabled (TxCEN bit reset) to

prevent any output state change and counter reset, except if they are used as ADC triggers.

Additionally, it is possible to enable digital noise filters, for external events 6 to 10, using

EExF[3:0] bits in the HRTIM_EECR3 register.

A digital filter is made of a counter in which a number N of valid samples is needed to

validate a transition on the output. If the input value changes before the counter has

reached the value N, the counter is reset and the transition is discarded (considered as a

spurious event). If the counter reaches N, the transition is considered as valid and

MSv48375V1

Timer A..E

Output

stage

Timer A..E

Output

stage

Timer A..E

Output

stage

Timer A..E

Output

stage

00

0

Digital

Filter

Source

selection

Edge and

polarity

Filtering

(EEV6..10 only)

Fast path

(EEV1..5 only)

Synchronous

path

EExFAST = 0

Fast asynchronous path

EExFAST = 1

EExSRC[1:0]

EExPOL

EExSNS[1:0]

1

!00

01

EExF[3:0]

Prescaler

EEVSD[1:0]

Timer A..F

Output

stage

Other EEVNT channels

9

10

11

EEVx_muxout

(to FAULT circuitry)

hrtim_eevx[4:1]

Loading...

Loading...