RM0440 Rev 4 1617/2126

RM0440 Universal synchronous/asynchronous receiver transmitter (USART/UART)

1733

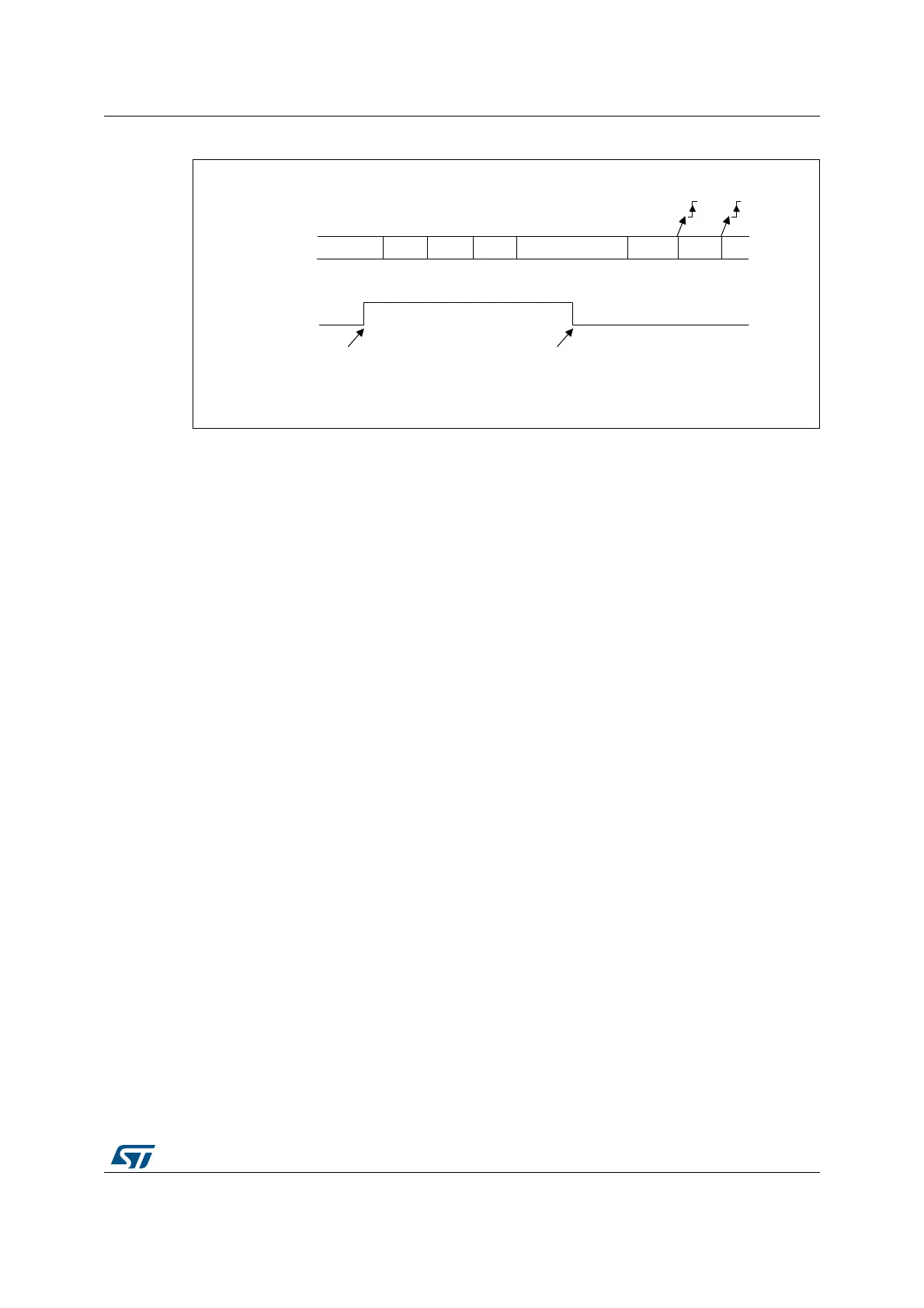

Figure 538. Mute mode using Idle line detection

Note: If the MMRQ is set while the IDLE character has already elapsed, Mute mode is not entered

(RWU is not set).

If the USART is activated while the line is IDLE, the idle state is detected after the duration

of one IDLE frame (not only after the reception of one character frame).

4-bit/7-bit address mark detection (WAKE=1)

In this mode, bytes are recognized as addresses if their MSB is a ‘1’, otherwise they are

considered as data. In an address byte, the address of the targeted receiver is put in the 4

or 7 LSBs. The choice of 7 or 4 bit address detection is done using the ADDM7 bit. This 4-

bit/7-bit word is compared by the receiver with its own address which is programmed in the

ADD bits in the USART_CR2 register.

Note: In 7-bit and 9-bit data modes, address detection is done on 6-bit and 8-bit addresses

(ADD[5:0] and ADD[7:0]) respectively.

The USART enters Mute mode when an address character is received which does not

match its programmed address. In this case, the RWU bit is set by hardware. The RXNE

flag is not set for this address byte and no interrupt or DMA request is issued when the

USART enters Mute mode. When FIFO management is enabled, the software should

ensure that there is at least one empty location in the RXFIFO before entering Mute mode.

The USART also enters Mute mode when the MMRQ bit is written to 1. The RWU bit is also

automatically set in this case.

The USART exits from Mute mode when an address character is received which matches

the programmed address. Then the RWU bit is cleared and subsequent bytes are received

normally. The RXNE/RXFNE bit is set for the address character since the RWU bit has been

cleared.

Note: When FIFO management is enabled, when MMRQ is set while the receiver is sampling last

bit of a data, this data may be received before effectively entering in Mute mode

An example of Mute mode behavior using address mark detection is given in Figure 539.

MSv31154V1

Data 1

Data 2 IDLEData 3 Data 4 Data 6

Idle frame detectedMMRQ written to 1

RWU

RX

Mute mode

Normal mode

RXNE RXNE

Data 5

Loading...

Loading...