Serial peripheral interface / integrated interchip sound (SPI/I2S) RM0440

1742/2126 RM0440 Rev 4

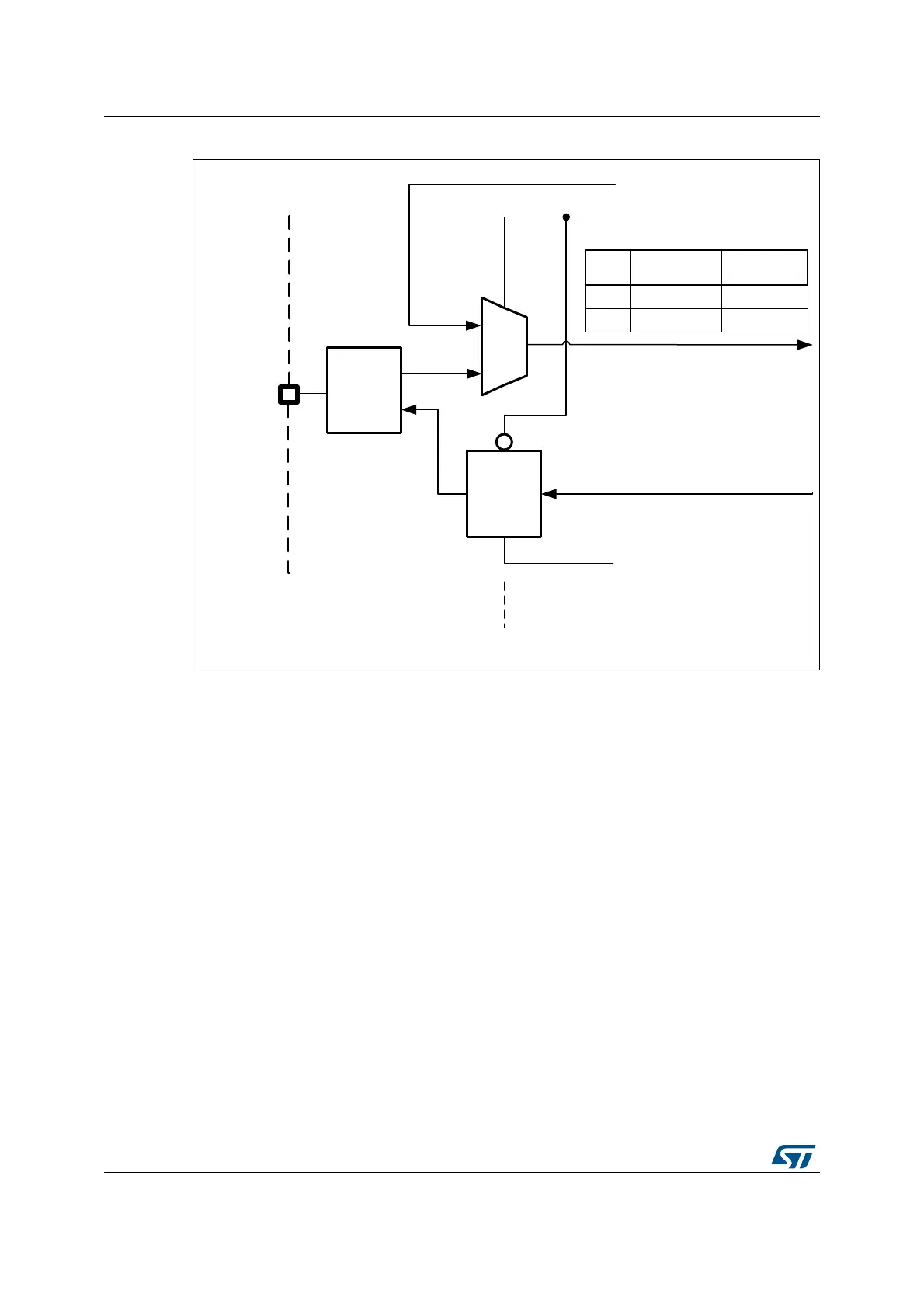

Figure 577. Hardware/software slave select management

39.5.6 Communication formats

During SPI communication, receive and transmit operations are performed simultaneously.

The serial clock (SCK) synchronizes the shifting and sampling of the information on the data

lines. The communication format depends on the clock phase, the clock polarity and the

data frame format. To be able to communicate together, the master and slaves devices must

follow the same communication format.

Clock phase and polarity controls

Four possible timing relationships may be chosen by software, using the CPOL and CPHA

bits in the SPIx_CR1 register. The CPOL (clock polarity) bit controls the idle state value of

the clock when no data is being transferred. This bit affects both master and slave modes. If

CPOL is reset, the SCK pin has a low-level idle state. If CPOL is set, the SCK pin has a

high-level idle state.

If the CPHA bit is set, the second edge on the SCK pin captures the first data bit transacted

(falling edge if the CPOL bit is reset, rising edge if the CPOL bit is set). Data are latched on

each occurrence of this clock transition type. If the CPHA bit is reset, the first edge on the

SCK pin captures the first data bit transacted (falling edge if the CPOL bit is set, rising edge

if the CPOL bit is reset). Data are latched on each occurrence of this clock transition type.

The combination of CPOL (clock polarity) and CPHA (clock phase) bits selects the data

capture clock edge.

1

0

NSS Input

SSM control bit

SSI control bit

SSOE control bit

NSS Output

NSS

pin

(used in Master mode and NSS

HW management only)

NSS

Output

Control

Master

mode

Slave mode

Non activeOKVdd

NSS

Inp.

ActiveConflictVss

NSS external logic

NSS internal logic

GPIO

logic

MSv35526V6

Loading...

Loading...