High-resolution timer (HRTIM) RM0440

884/2126 RM0440 Rev 4

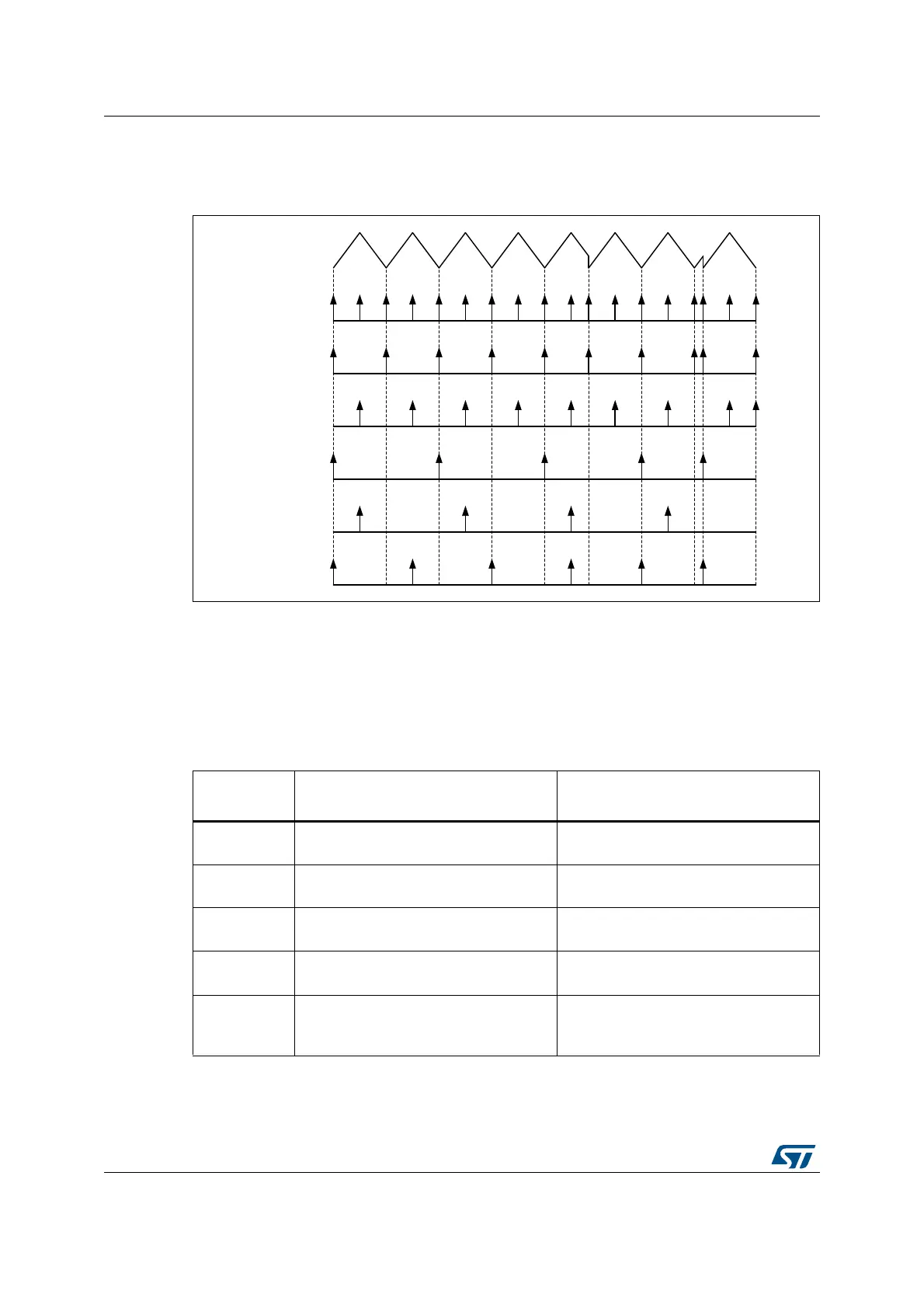

Figure 214 below shows how the repetition counter is decremented in up-down counting

mode.

Figure 214. Repetition counter behavior in up-down counting mode

The dual channel DAC triggers are working as for the up-counting mode.

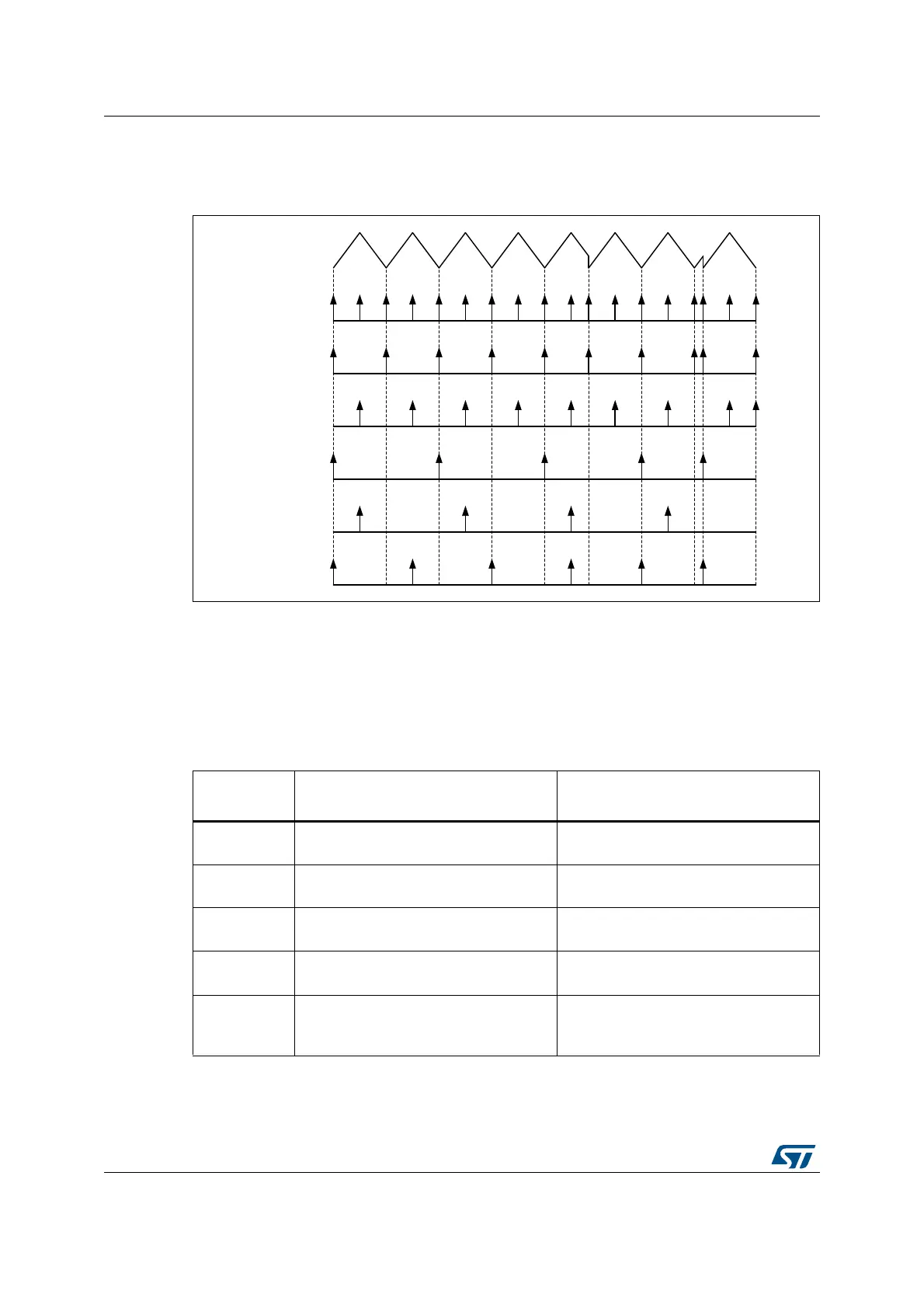

The event blanking and windowing differs so as to have the blanking or windowing done

within the output pulse, at a programmable time. The EExFLTR[3:0] codes are depending

on the UDM bit setting, as per the Table 221 below. Whenever the roll-over event is used for

blanking or windowing, the ROM[1:0] programming applies for defining when it is

generated.

Table 221. EExFLTR[3:0] codes depending on UDM bit setting

EE1FLTR[3:0]

Up-counting mode

(UDM = 0)

Up/down-counting mode

(UDM = 1)

0010

Blanking from counter reset/roll-over to

compare 2

Blanking from compare 1 to compare 2,

only during the up-counting phase

0100

Blanking from counter reset/roll-over to

compare 4

Blanking from compare 3 to compare 4,

only during the up-counting phase

1101

Windowing from counter reset/roll-over

to compare 2

Windowing from compare 2 to compare

3, only during the up-counting phase

1110

Windowing from counter reset/roll-over

to compare 3

Windowing from compare 2 to compare

3, only during the down-counting phase

1111

Windowing from another timing unit:

TIMWIN source (see Table 19 for details)

Windowing from compare 2 during the

up-counting phase to compare 3 during

the down-counting phase

MSv47421V1

REP = 2

ROM[1:0] = 00

REP = 1

ROM[1:0] = 10

REP = 1

ROM[1:0] = 01

REP = 0

ROM[1:0] = 10

REP = 0

ROM[1:0] = 01

REP = 0

ROM[1:0] = 00

Counter

Loading...

Loading...