RM0440 Rev 4 1167/2126

RM0440 Advanced-control timers (TIM1/TIM8/TIM20)

1226

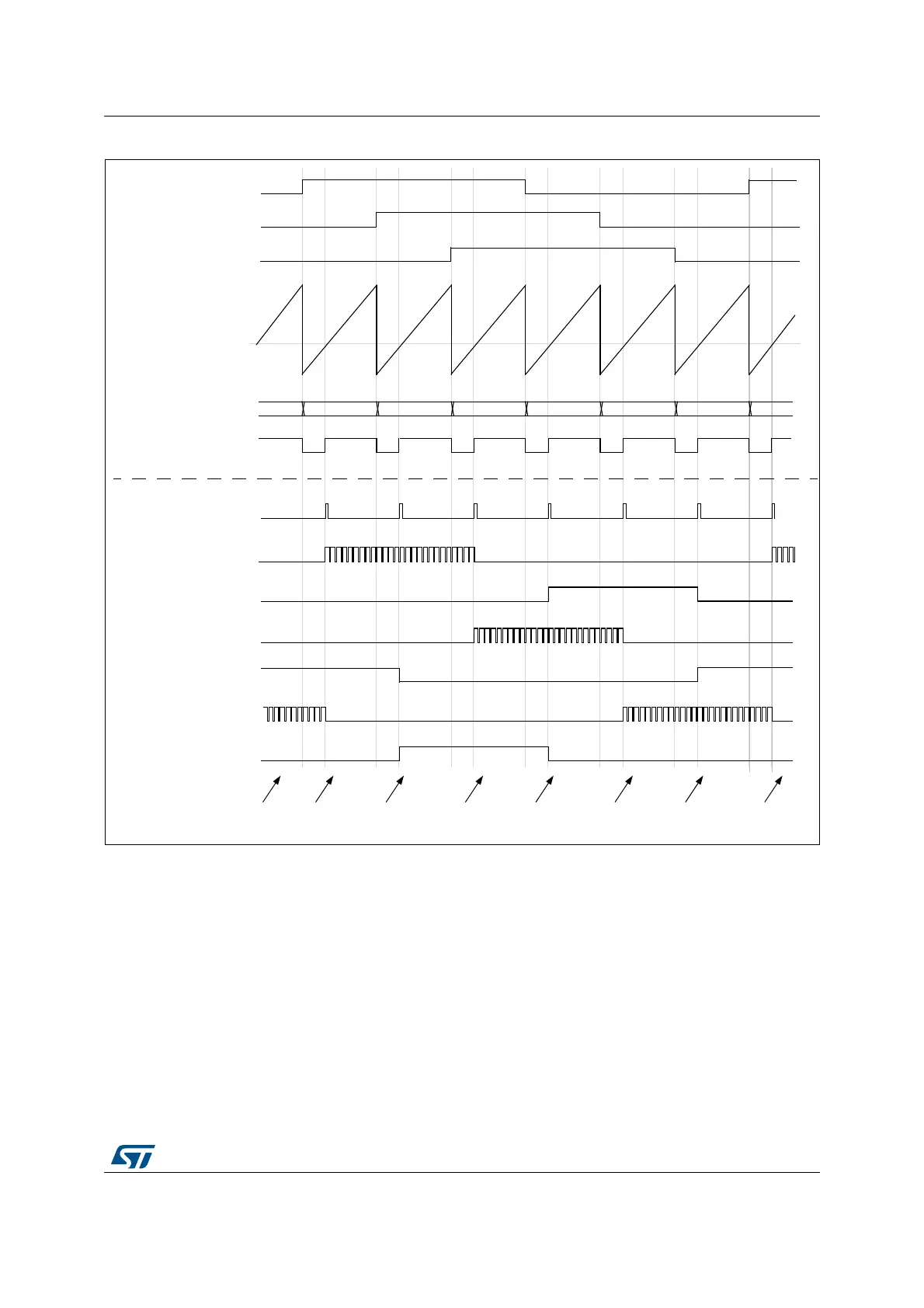

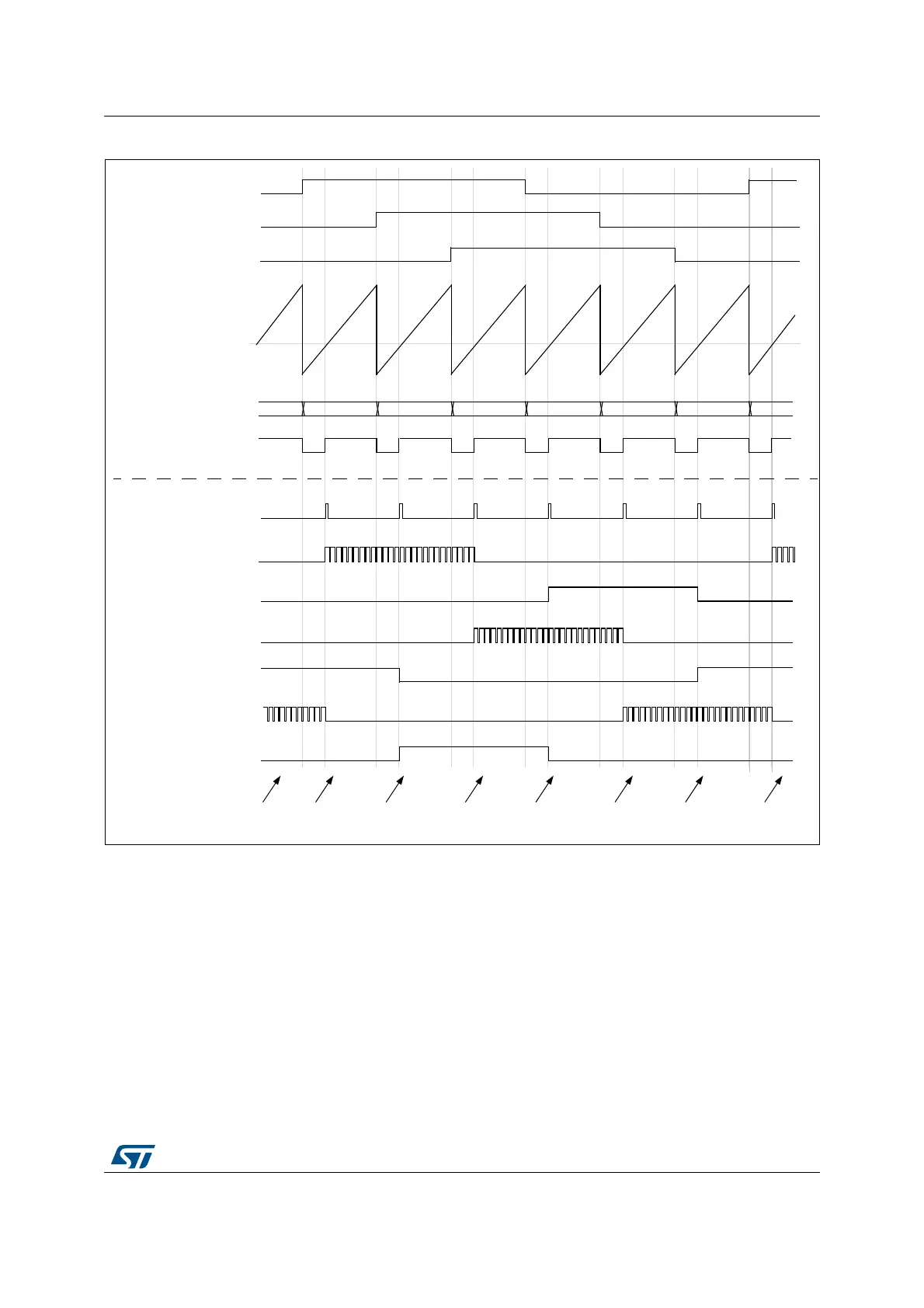

Figure 353. Example of Hall sensor interface

28.3.30 Timer synchronization

The TIMx timers are linked together internally for timer synchronization or chaining. Refer to

Section 29.4.23: Timer synchronization for details. They can be synchronized in several

modes: Reset mode, Gated mode, Trigger mode, Reset + trigger and gated + reset modes.

Slave mode: Reset mode

The counter and its prescaler can be reinitialized in response to an event on a trigger input.

Moreover, if the URS bit from the TIMx_CR1 register is low, an update event UEV is

generated. Then all the preloaded registers (TIMx_ARR, TIMx_CCRx) are updated.

MSv62360V1

tim_oc3n

tim_oc3

tim_oc2n

tim_oc2

tim_oc1n

tim_oc1

COM

tim_trgo = tim_oc2ref

tim_ti1

tim_ti2

tim_ti3

Advanced-control timers

Write CCxE, CCxNE

and OCxM for next step

Interfacing timer

Counter (CNT)

(CCR2)

CCR1)

C7A3 C7A8 C794 C7A5 C7AB C796

Loading...

Loading...