RM0440 Rev 4 655/2126

RM0440 Analog-to-digital converters (ADC)

724

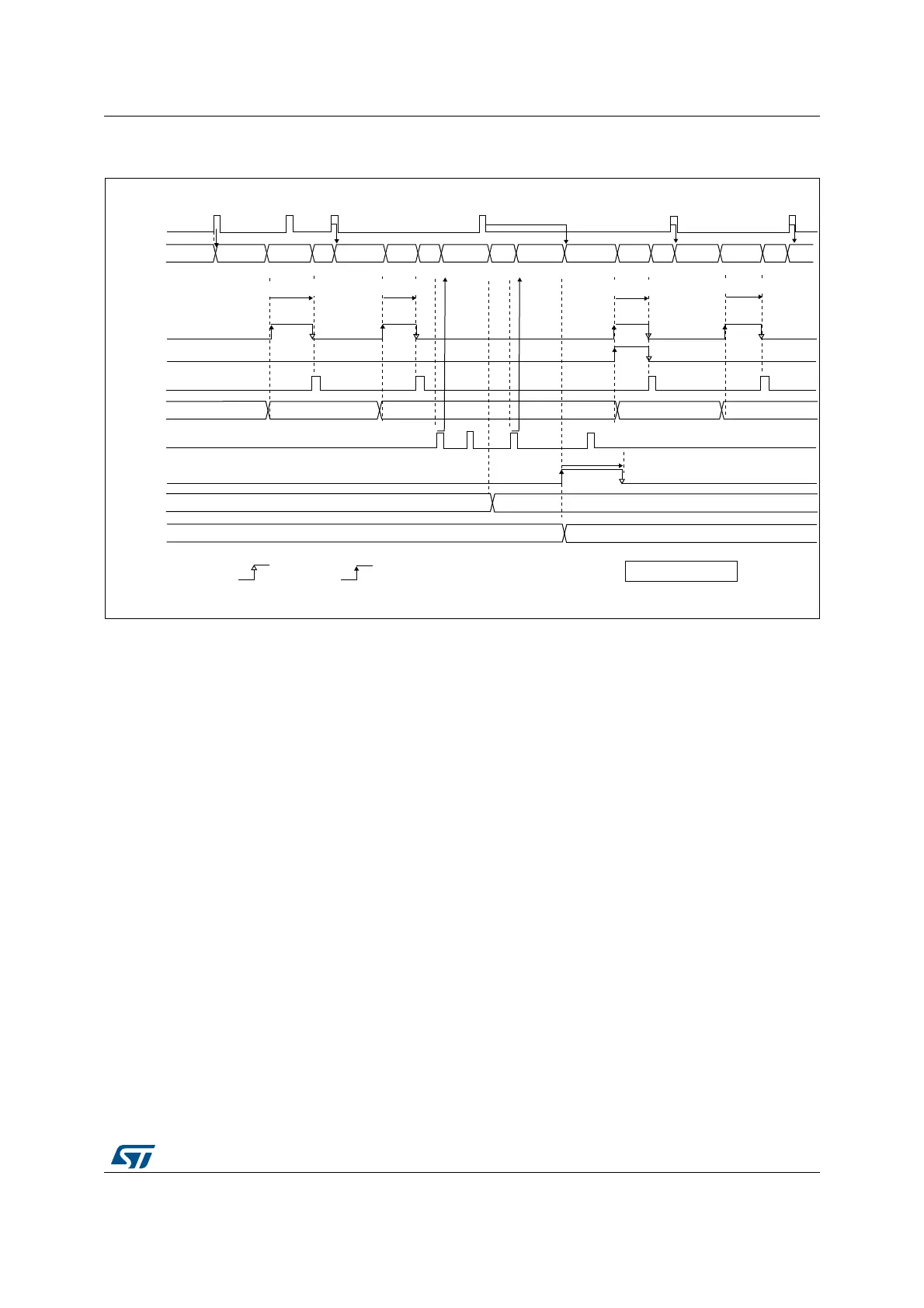

Figure 122. AUTODLY=1, regular HW conversions interrupted by injected conversions

(DISCEN=1, JDISCEN=1)

1. AUTDLY=1

2. Regular configuration: EXTEN[1:0]=01 (HW trigger), CONT=0, DISCEN=1, DISCNUM=1, CHANNELS = 1, 2, 3.

3. Injected configuration: JEXTEN[1:0]=01 (HW Trigger), JDISCEN=1, CHANNELS = 5,6

Ignored

Ignored

MS31022V1

Injected

trigger

regular

JEOS

ADC_JDR1

ADC_JDR2

Regular

trigger

injected

regular

regular

DLY (CH1)

DLY (inj)

Not ignored

(occurs during injected sequence)

Ignored

regular

DLY (CH2)

ADC_DR

EOC

EOS

ADC

state

ADC_DR read access

by s/w by h/w

Indicative timings

RDY

CH1

DLY

DLY

RDY

CH2

RDY

CH5

CH6

CH3

RDY

D1

D1

D2 D3

DLY

D6

D5

regular

injected

RDY CH1

DLY

RDY

CH2

DLY (CH3)

DLY (CH1)

Loading...

Loading...