RM0440 Rev 4 659/2126

RM0440 Analog-to-digital converters (ADC)

724

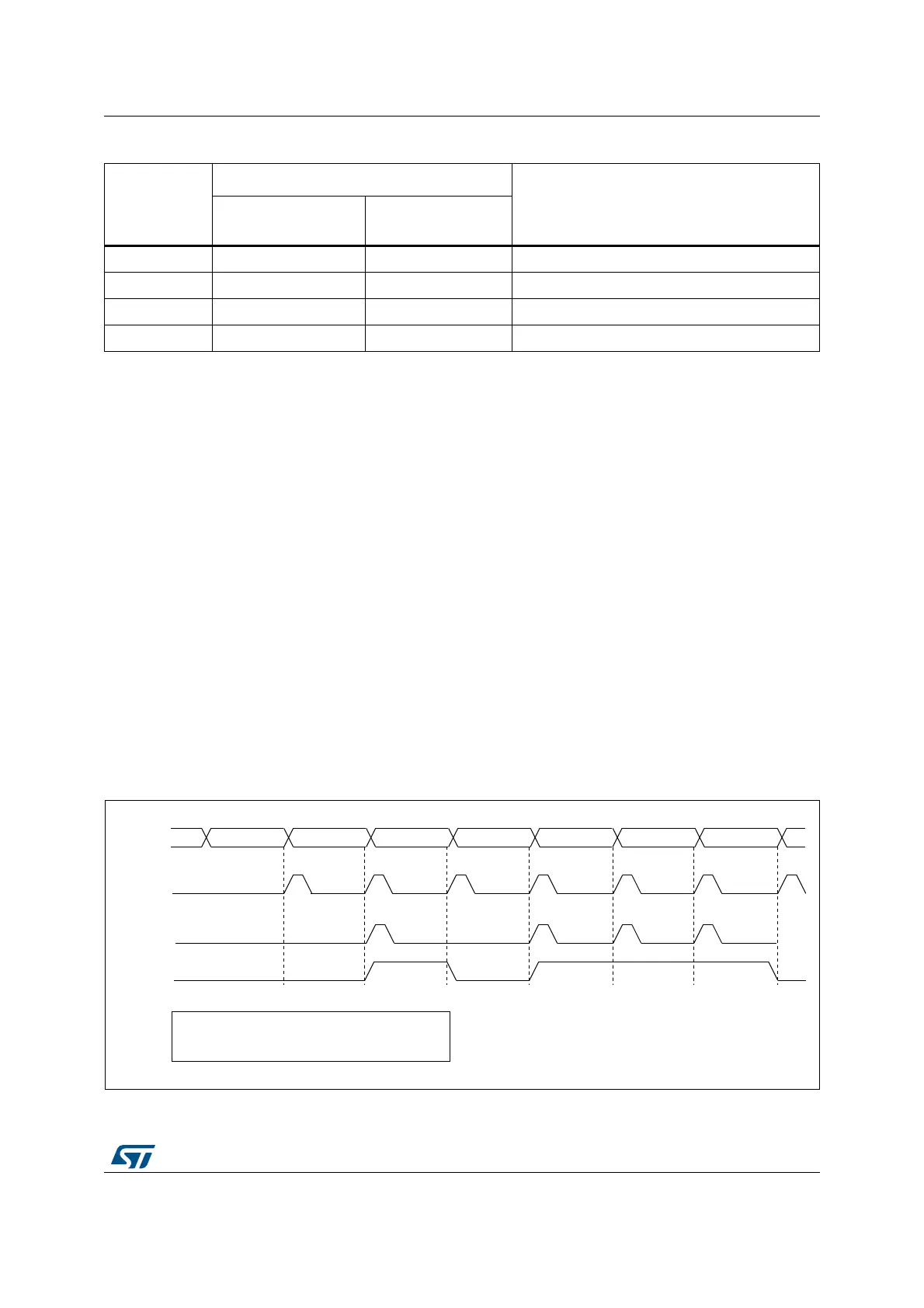

ADCy_AWDx_OUT signal output generation

Each analog watchdog is associated to an internal hardware signal ADCy_AWDx_OUT

(y=ADC number, x=watchdog number) which is directly connected to the ETR input

(external trigger) of some on-chip timers. Refer to the on-chip timers section to understand

how to select the ADCy_AWDx_OUT signal as ETR.

ADCy_AWDx_OUT is activated when the associated analog watchdog is enabled:

• ADCy_AWDx_OUT is set when a guarded conversion is outside the programmed

thresholds.

• ADCy_AWDx_OUT is reset after the end of the next guarded conversion which is

inside the programmed thresholds (It remains at 1 if the next guarded conversions are

still outside the programmed thresholds).

• ADCy_AWDx_OUT is also reset when disabling the ADC (when setting ADDIS=1).

Note that stopping regular or injected conversions (setting ADSTP=1 or JADSTP=1)

has no influence on the generation of ADCy_AWDx_OUT.

Note: AWDx flag is set by hardware and reset by software: AWDx flag has no influence on the

generation of ADCy_AWDx_OUT (ex: ADCy_AWDx_OUT can toggle while AWDx flag

remains at 1 if the software did not clear the flag).

Figure 126. ADCy_AWDx_OUT signal generation (on all regular channels)

Table 171. Analog watchdog 2 and 3 comparison

Resolution

(bits RES[1:0])

Analog watchdog comparison between:

Comments

Raw converted data,

left aligned

(1)

Thresholds

00: 12-bit DATA[11:4] LTx[7:0] and HTx[7:0] DATA[3:0] are not relevant for the comparison

01: 10-bit DATA[11:4] LTx[7:0] and HTx[7:0] DATA[3:2] are not relevant for the comparison

10: 8-bit DATA[11:4] LTx[7:0] and HTx[7:0] -

11: 6-bit DATA[11:6],00 LTx[7:0] and HTx[7:0] User must configure LTx[1:0] and HTx[1:0] to 00

1. Refer to Section : Gain compensation for additional details on analog watchdog comparison.

EOC FLAG

ADC

STATE

RDY

AWDx FLAG

Conversion1

outside

ADCy_AWDx_OUT

inside

cleared

by S/W

- Converting regular channels 1,2,3,4,5,6,7

- Regular channels 1,2,3,4,5,6,7 are all guarded

MS31025V1

Conversion2 Conversion3 Conversion4 Conversion5 Conversion6 Conversion7

outsideinside outside outside inside

cleared

by S/W

cleared

by S/W

cleared

by S/W

Loading...

Loading...