Analog-to-digital converters (ADC) RM0440

670/2126 RM0440 Rev 4

Injected simultaneous mode

This mode is selected by programming bits DUAL[4:0]=00101

This mode converts an injected group of channels. The external trigger source comes from

the injected group multiplexer of the master ADC (selected by the JEXTSEL bits

in the

ADC_JSQR register).

Note: Do not convert the same channel on the two ADCs (no overlapping sampling times for the

two ADCs when converting the same channel).

In simultaneous mode, one must convert sequences with the same length or ensure that the

interval between triggers is longer than the longer of the 2 sequences. Otherwise, the ADC

with the shortest sequence may restart while the ADC with the longest sequence is

completing the previous conversions.

Regular conversions can be performed on one or all ADCs. In that case, they are

independent of each other and are interrupted when an injected event occurs. They are

resumed at the end of the injected conversion group.

• At the end of injected sequence of conversion event (JEOS) on the master ADC, the

converted data is stored into the master ADC_JDRy registers and a JEOS interrupt is

generated (if enabled)

• At the end of injected sequence of conversion event (JEOS) on the slave ADC, the

converted data is stored into the slave ADC_JDRy registers and a JEOS interrupt is

generated (if enabled)

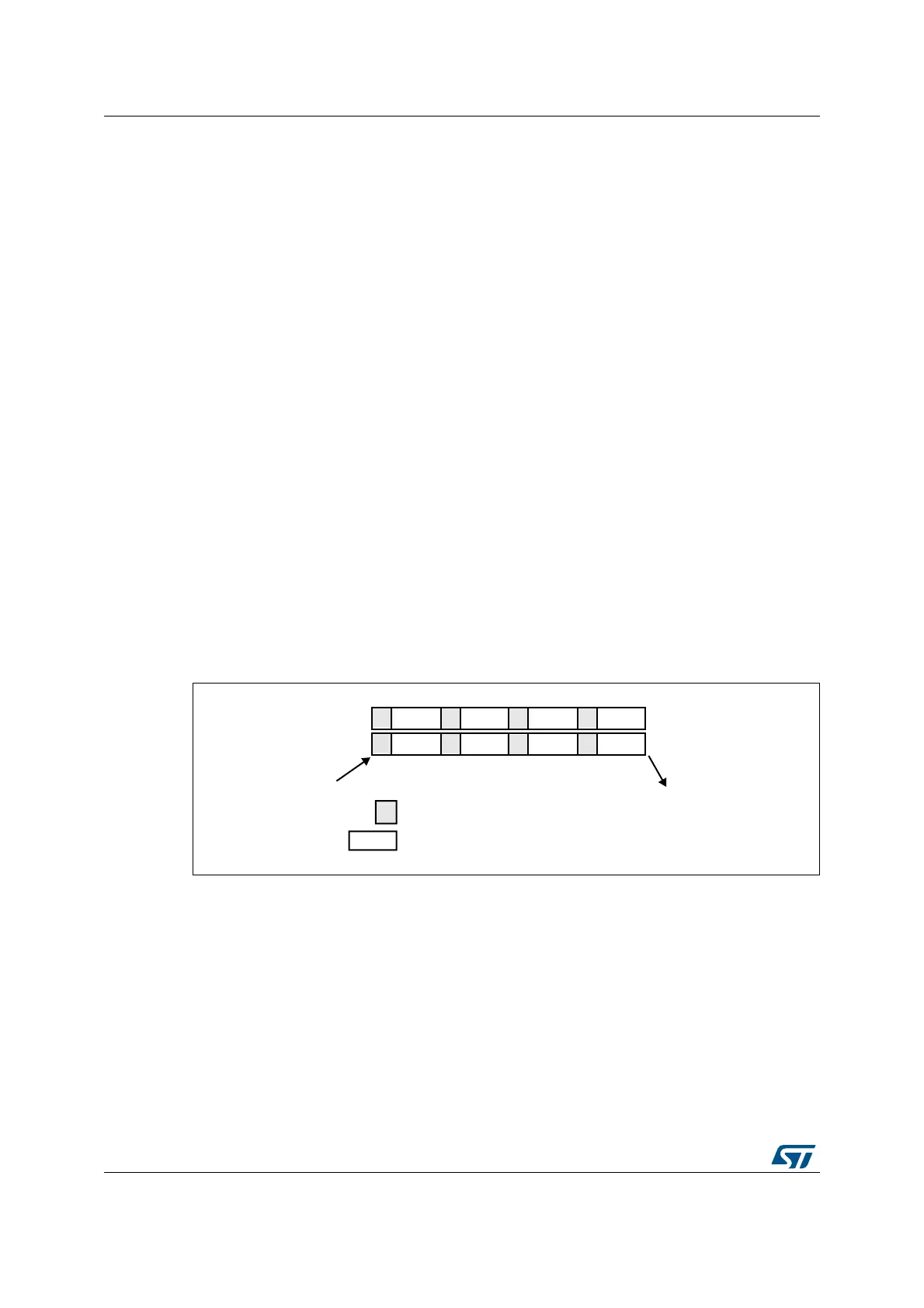

• If the duration of the master injected sequence is equal to the duration of the slave

injected one (like in Figure 138), it is possible for the software to enable only one of the

two JEOS interrupt (ex: master JEOS) and read both converted data (from master

ADC_JDRy and slave ADC_JDRy registers).

Figure 138. Injected simultaneous mode on 4 channels: dual ADC mode

If JDISCEN=1, each simultaneous conversion of the injected sequence requires an injected

trigger event to occur.

This mode can be combined with AUTDLY mode:

• Once a simultaneous injected sequence of conversions has ended, a new injected

trigger event is accepted only if both JEOS bits of the master and the slave ADC have

been cleared (delay phase). Any new injected trigger events occurring during the

ongoing injected sequence and the associated delay phase are ignored.

• Once a regular sequence of conversions of the master ADC has ended, a new regular

trigger event of the master ADC is accepted only if the master data register (ADC_DR)

has been read. Any new regular trigger events occurring for the master ADC during the

MASTER ADC

SLAVE ADC

End of injected sequence on

MASTER and SLAVE ADC

MS31900V1

Trigger

CH1

CH15 CH14 CH13 CH12

CH2 CH3 CH4

Sampling

Conversion

Loading...

Loading...