RM0440 Rev 4 1517/2126

RM0440 AES hardware accelerator (AES)

1538

CCM processing

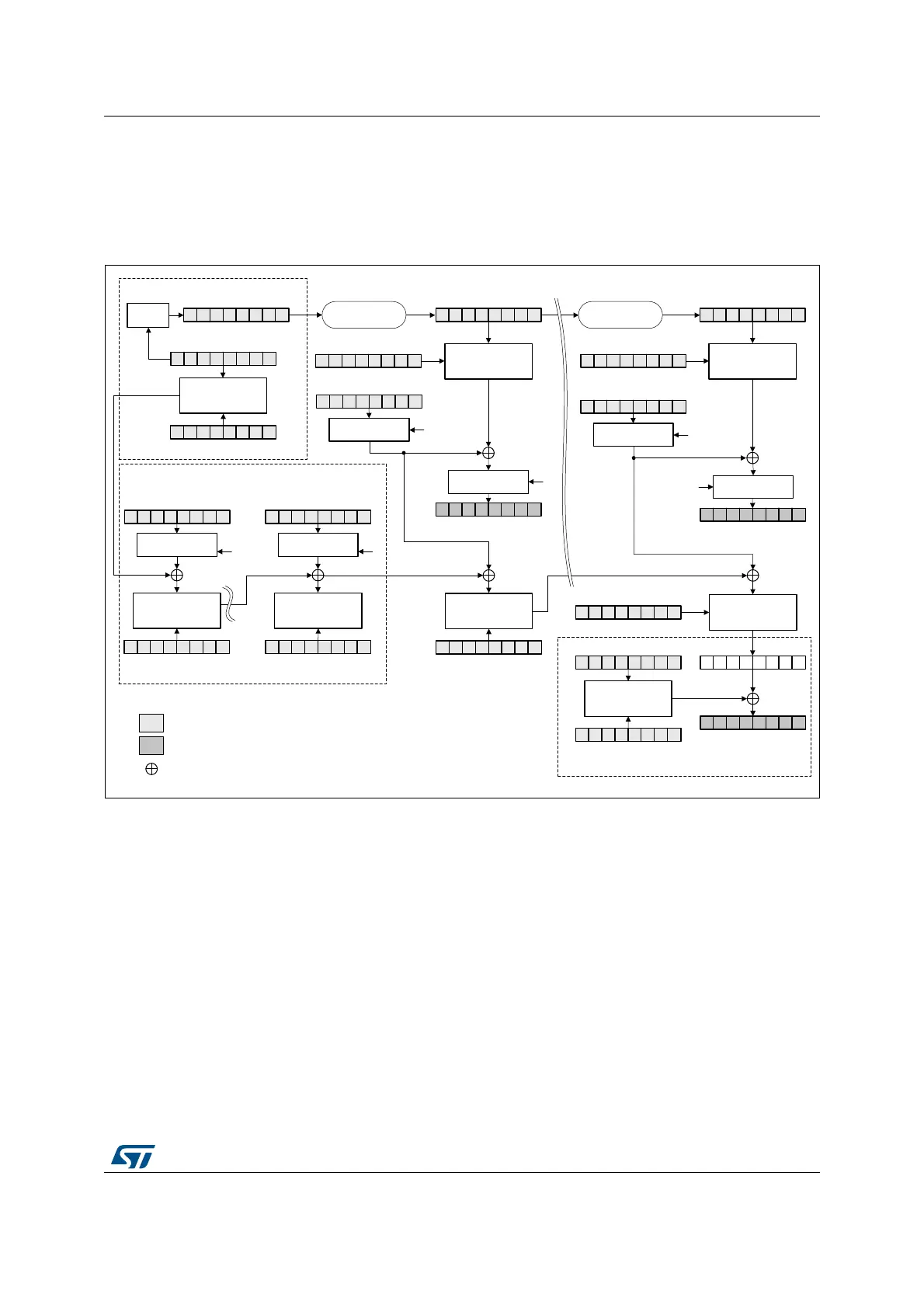

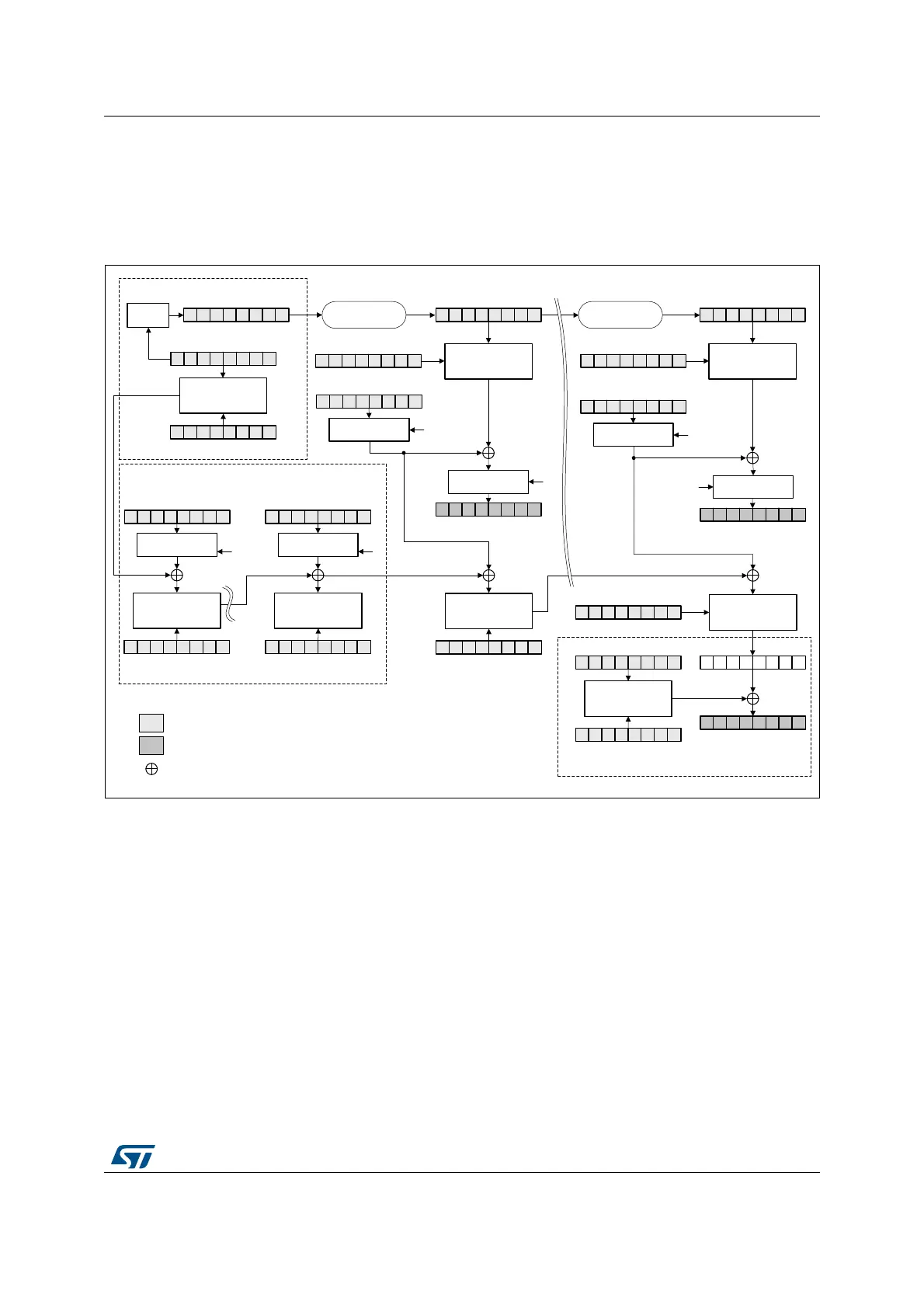

Figure 524 describes the CCM implementation within the AES peripheral (encryption

example). This mode is selected by writing 100 into the CHMOD[2:0] bitfield of the AES_CR

register.

Figure 524. CCM mode authenticated encryption

The data input to the generation-encryption process are a valid nonce, a valid payload

string, and a valid associated data string, all properly formatted. The CBC chaining

mechanism is applied to the formatted plaintext data to generate a MAC, with a known

length. Counter mode encryption that requires a sufficiently long sequence of counter blocks

as input, is applied to the payload string and separately to the MAC. The resulting ciphertext

C is the output of the generation-encryption process on plaintext P.

AES_IVRx registers are used for processing each data block, AES automatically

incrementing the CTR counter with a bit length defined by the first block B0. Table 322

shows how the application must load the B0 data.

Note: The AES peripheral in CCM mode supports counters up to 64 bits, as specified by NIST.

MSv42152V1

(2) Header

(1) Init

(4) Final

AES_DINR (plaintext P1)

AES_DOUTR (ciphertext C1)

DATATYPE

[1:0]

Swap

management

AES_IVRx (CTR1)

input

output

Legend

XOR

Swap

management

DATATYPE

[1:0]

AES_KEYRx (KEY)

AES_IVRx (CTRm)

Swap

management

DATATYPE

[1:0]

Counter

increment (+1)

AES_DINR (plaintext

last block Pm )

AES_DOUTR

(ciphertext last block Cm)

Encrypt

AES_IVRx (CTR0)

AES_DINR (associated

data block B1)

Swap

management

Swap

management

AES_DINR (associated

data last block Bu)

AES_KEYRx (KEY)

AES_DINR (CTR0)

Encrypt

AES_KEYRx (KEY)

AES_DOUTR

(EncTAG)

MAC (T)

Encrypt Encrypt

S0

B

r

B

u+1

Encrypt

AES_KEYRx (KEY)

Encrypt

AES_KEYRx (KEY)

Encrypt

AES_KEYRx (KEY)

Encrypt

AES_KEYRx (KEY)

AES_KEYRx (KEY)

DATATYPE

[1:0]

Swap

management

DATATYPE[1:0]

DATATYPE[1:0]

Sm

S1

Counter

increment (+1)

AES_IVRx (First block B0)

mask

Block 1 Block m

(3) Payload

Loading...

Loading...