RM0440 Rev 4 1449/2126

RM0440 Basic timers (TIM6/TIM7)

1463

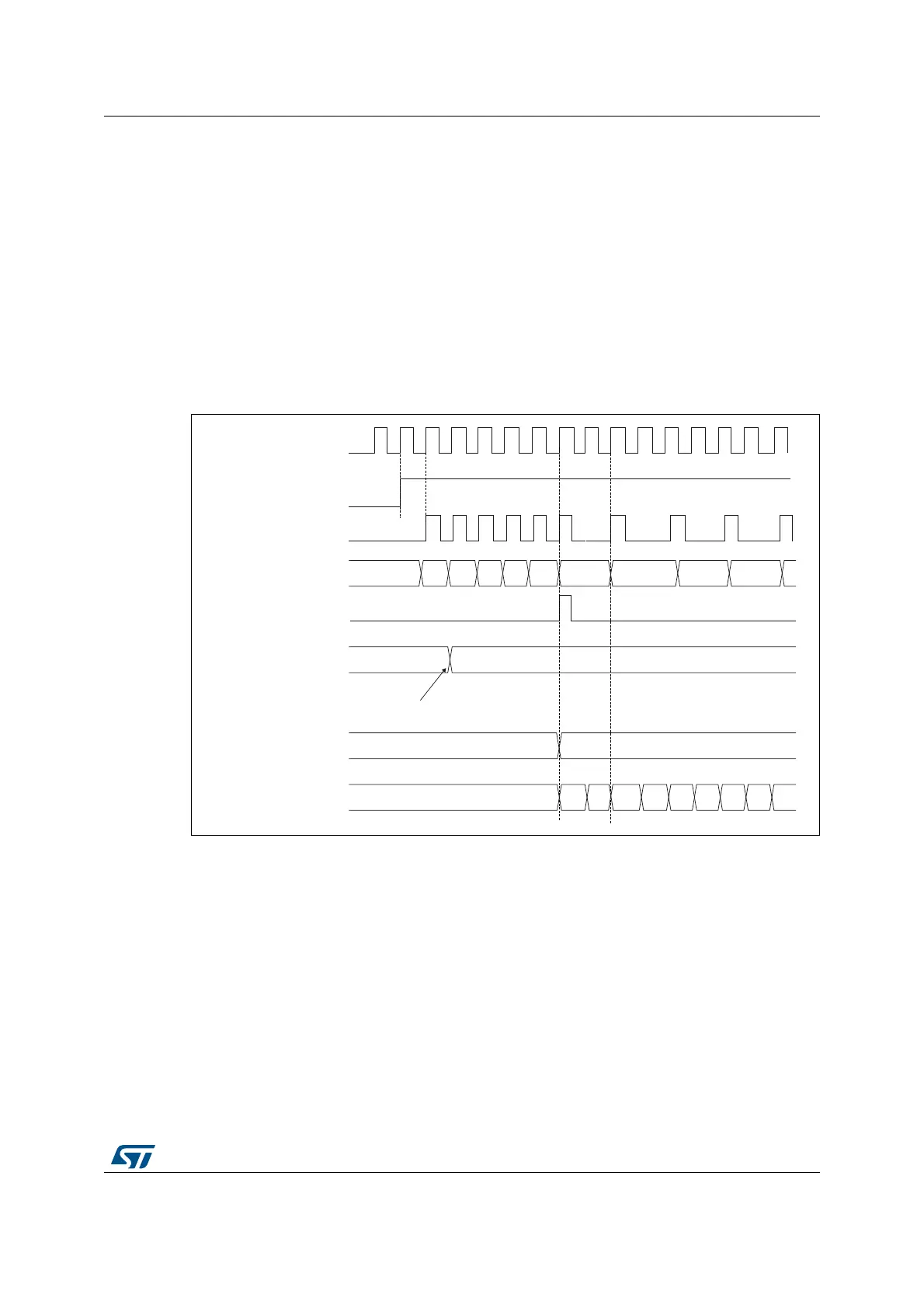

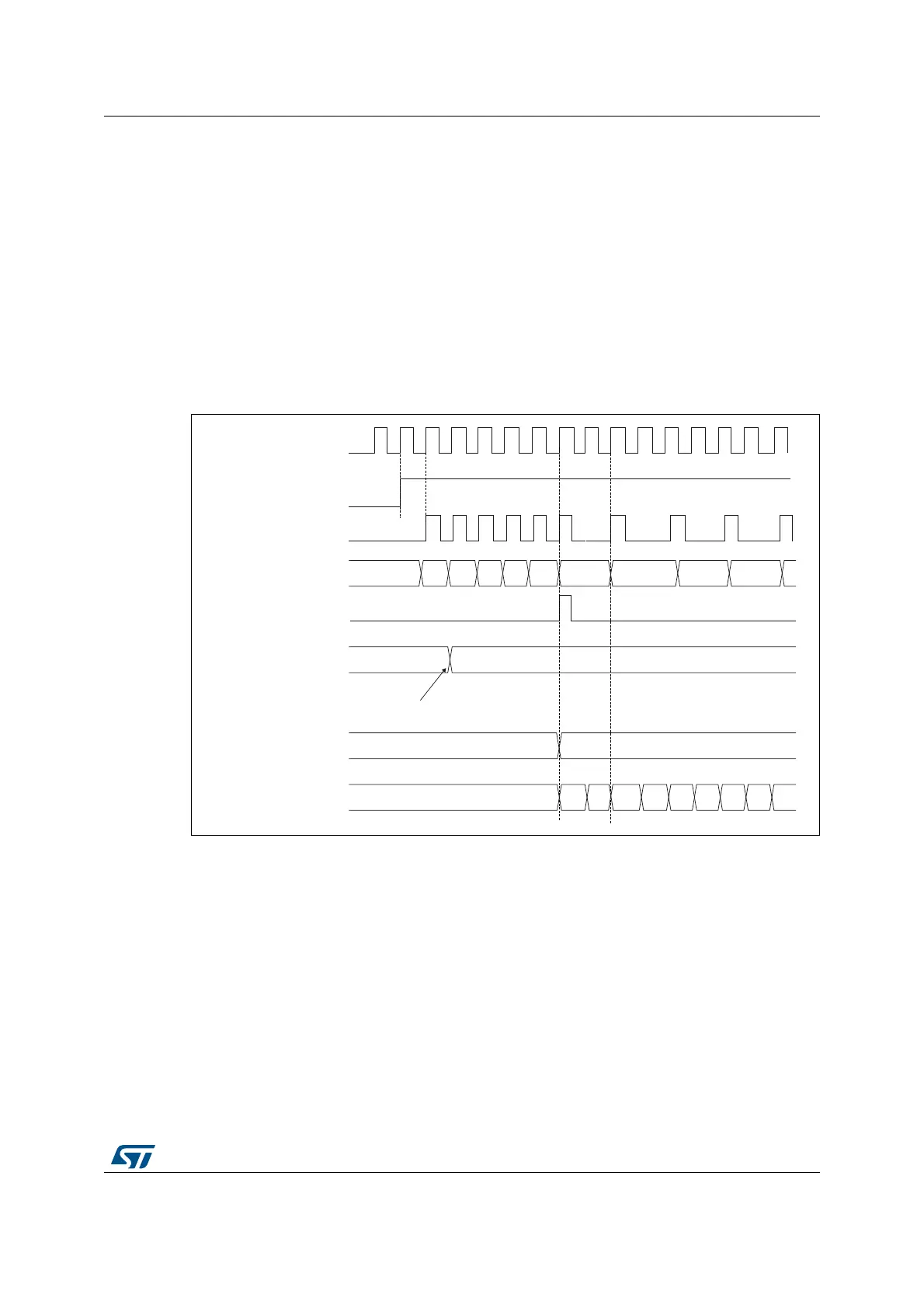

The counter is clocked by the prescaler output tim_cnt_ck, which is enabled only when the

counter enable bit (CEN) in the TIMx_CR1 register is set.

Note that the actual counter enable signal tim_cnt_en is set 1 clock cycle after CEN bit set.

Prescaler description

The prescaler can divide the counter clock frequency by any factor between 1 and 65536. It

is based on a 16-bit counter controlled through a 16-bit register (in the TIMx_PSC register).

It can be changed on the fly as the TIMx_PSC control register is buffered. The new

prescaler ratio is taken into account at the next update event.

Figure 481 and Figure 482 give some examples of the counter behavior when the prescaler

ratio is changed on the fly.

Figure 481. Counter timing diagram with prescaler division change from 1 to 2

MSv50998V1

tim_psc_ck

00

CEN

Counter register

Update event (UEV)

0

Prescaler control register

1

0

Write a new value in TIMx_PSC

Prescaler buffer

1

0

Prescaler counter

0

10

10

1

0

1

01

02

03

FA

FBF7 F8 F9 FC

tim_cnt_ck

Loading...

Loading...