RM0440 Rev 4 377/2126

RM0440 System configuration controller (SYSCFG)

380

Note: Some of the I/O pins mentioned in the above register may not be available on small

packages.

10.2.7 SYSCFG CCM SRAM control and status register (SYSCFG_SCSR)

Address offset: 0x18

System reset value: 0x0000 0000

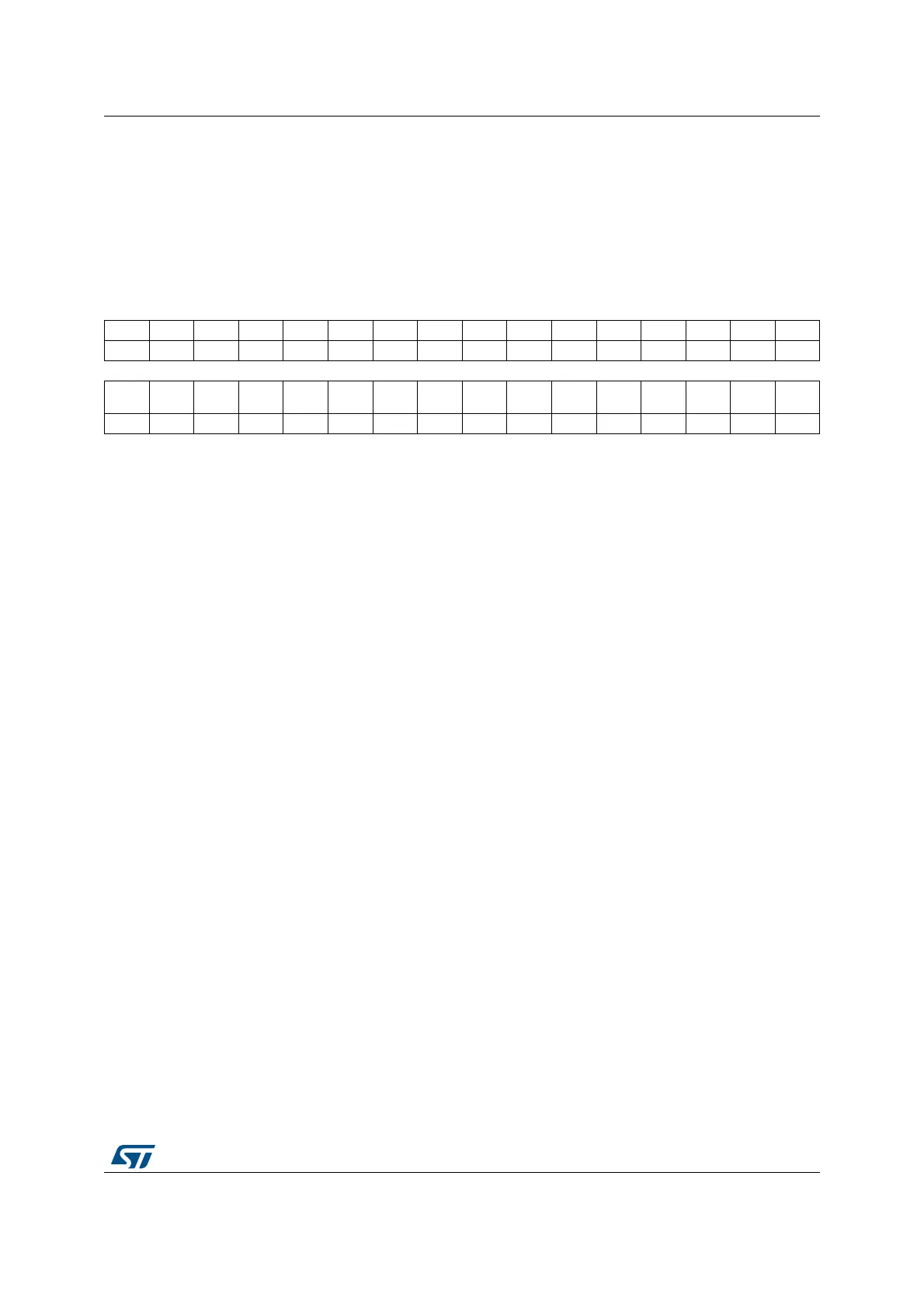

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res Res Res Res Res Res Res Res Res Res Res Res Res Res Res Res

1514131211109876543210

Res Res Res Res Res Res Res Res Res Res Res Res Res Res

CCM

BSY

CCM

ER

rrw

Bits 31:2 Reserved, must be kept at reset value

Bit 1 CCMBSY: CCM SRAM busy by erase operation

0: No CCM SRAM erase operation is on going.

1: CCM SRAM erase operation is on going.

Bit 0 CCMER: CCM SRAM Erase

Setting this bit starts a hardware CCM SRAM erase operation. This bit is

automatically cleared at the end of the CCM SRAM erase operation.

Note: This bit is write-protected: setting this bit is possible only after the correct

key sequence is written in the SYSCFG_SKR register.

Loading...

Loading...