System configuration controller (SYSCFG) RM0440

378/2126 RM0440 Rev 4

10.2.8 SYSCFG configuration register 2 (SYSCFG_CFGR2)

Address offset: 0x1C

System reset value: 0x0000 0000

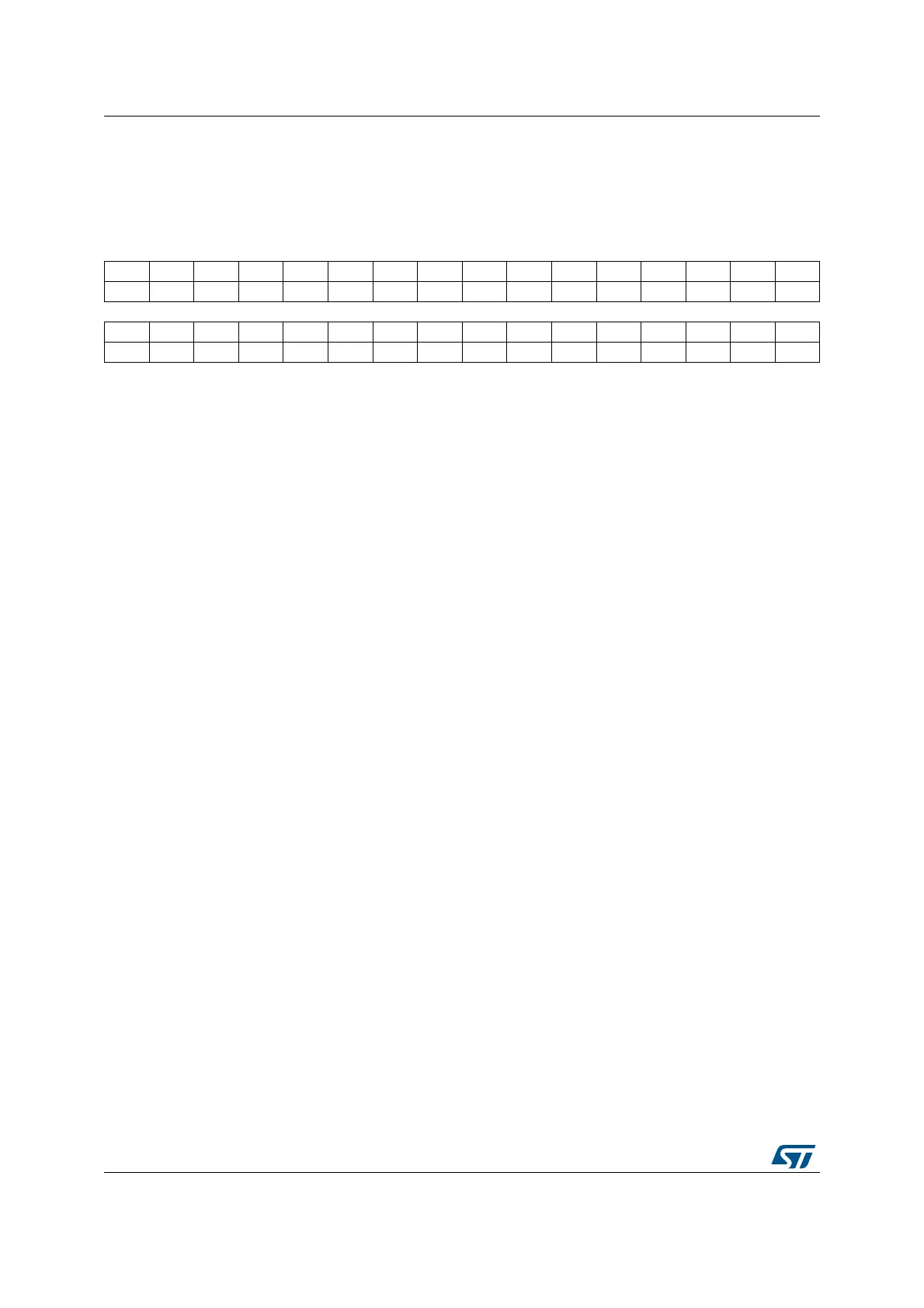

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res Res Res Res Res Res Res Res Res Res Res Res Res Res Res Res

1514131211109876543210

Res Res Res Res Res Res Res SPF Res Res Res Res ECCL PVDL SPL CLL

rc_w1 rsrsrsrs

Bits 31:9 Reserved, must be kept at reset value

Bit 8 SPF: SRAM1 and CCM SRAM parity error flag

This bit is set by hardware when an SRAM1 or CCM SRAM parity error is

detected. It is cleared by software by writing ‘1’.

0: No parity error detected

1: Parity error detected

Bits 7:4 Reserved, must be kept at reset value

Bit 3 ECCL: ECC Lock

This bit is set by software and cleared only by a system reset. It can be used to

enable and lock the Flash ECC error connection to TIM1/8/15/16/17/20 break

input and hrtim_sys_flt input of HRTIM1.

0: ECC error disconnected from TIM1/8/15/16/17/20 break input and

hrtim_sys_flt input of HRTIM1.

1: ECC error connected to TIM1/8/15/16/17/20 break input and hrtim_sys_flt

input of HRTIM1.

Bit 2 PVDL: PVD lock enable bit

This bit is set by software and cleared only by a system reset. It can be used to

enable and lock the PVD connection to TIM1/8/15/16/17/20 break input and

hrtim_sys_flt input of HRTIM1., as well as the PVDE and PLS[2:0] in the

PWR_CR2 register.

0: PVD interrupt disconnected from TIM1/8/15/16/17/20 break input and

hrtim_sys_flt input of HRTIM1. PVDE and PLS[2:0] bits can be programmed by

the application.

1: PVD interrupt connected to TIM1/8/15/16/17/20 break input and hrtim_sys_flt

input of HRTIM1, PVDE and PLS[2:0] bits are read only.

Bit 1 SPL: SRAM1 and CCM SRAM parity lock bit

This bit is set by software and cleared only by a system reset. It can be used to

enable and lock the SRAM1 or CCM SRAM parity error signal connection to

TIM1/8/15/16/17/20 break input and hrtim_sys_flt input of HRTIM1.

0: CCM SRAM parity error signal disconnected from TIM1/8/15/16/17/20 break

input and hrtim_sys_flt input of HRTIM1.

1: CCM SRAM parity error signal connected to TIM1/8/15/16/17/20 break input

and hrtim_sys_flt input of HRTIM1.

Loading...

Loading...