High-resolution timer (HRTIM) RM0440

1012/2126 RM0440 Rev 4

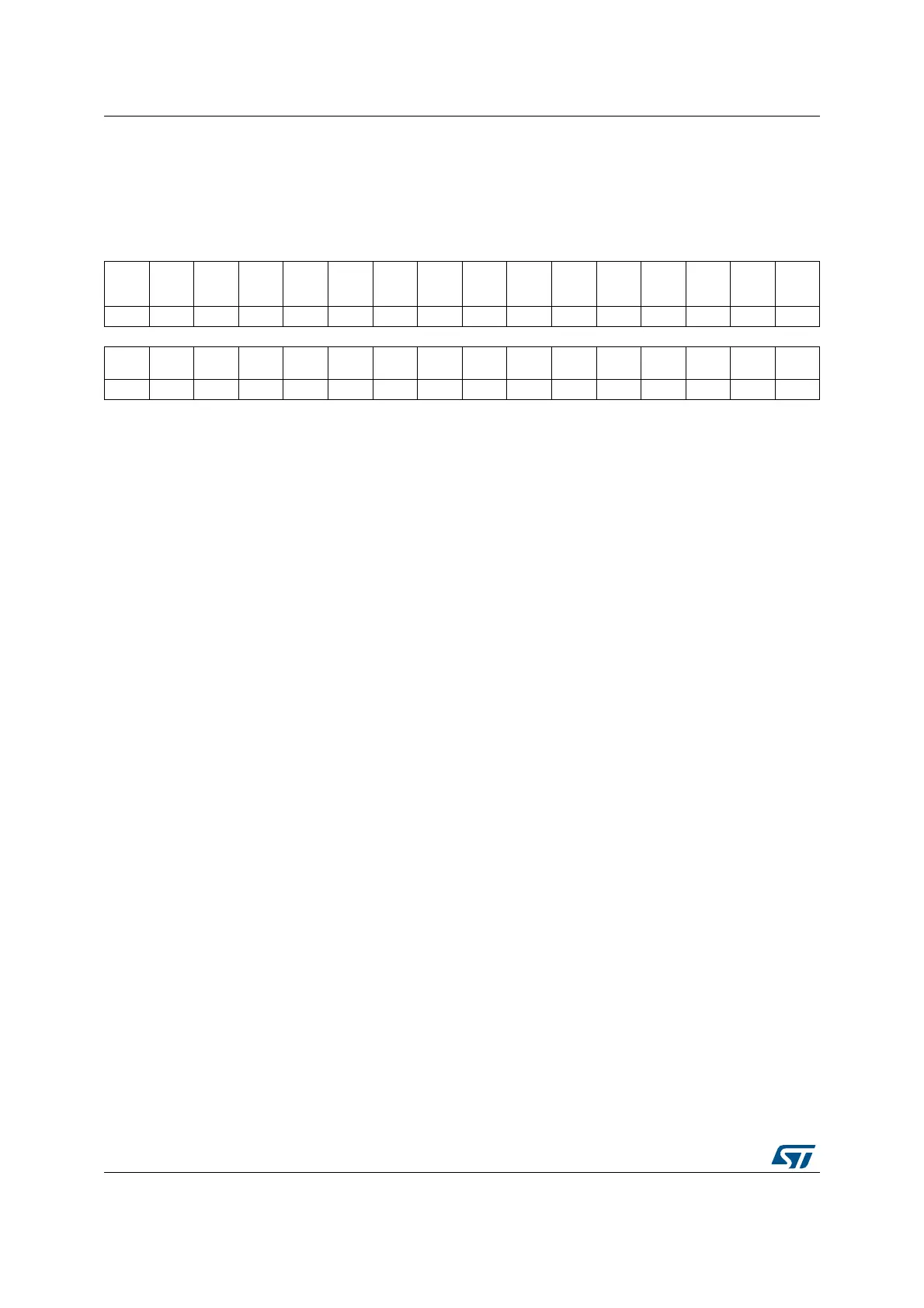

27.5.38 HRTIM timer F reset register (HRTIM_RSTFR)

Address offset: 0x354

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TIME

CMP2

TIMD

CMP4

TIMD

CMP2

TIMD

CMP1

TIMC

CMP4

TIMC

CMP2

TIMC

CMP1

TIMB

CMP4

TIMB

CMP2

TIMB

CMP1

TIMA

CMP4

TIMA

CMP2

TIMA

CMP1

EXT

EVNT

10

EXT

EVNT9

EXT

EVNT8

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

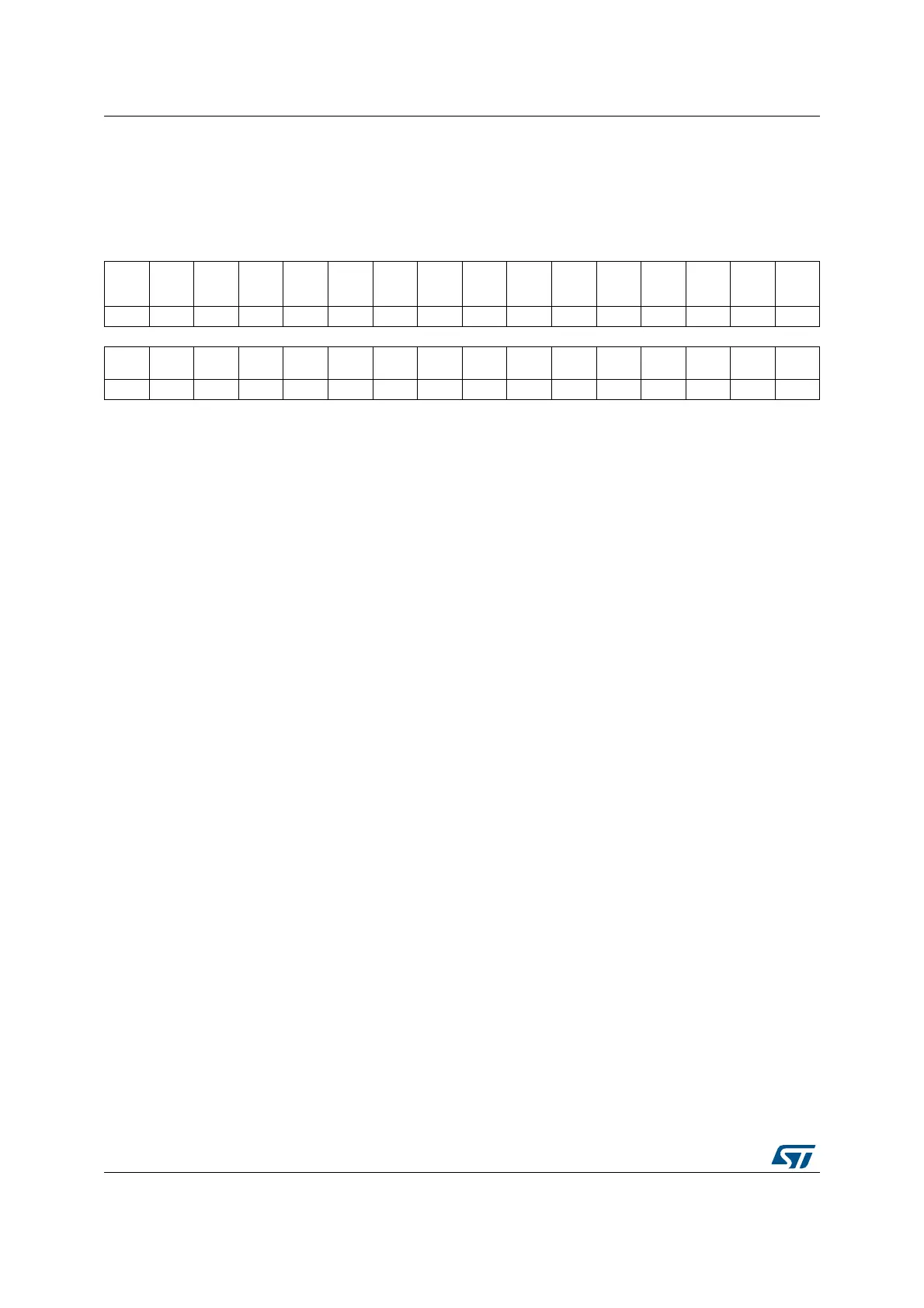

1514131211109876543210

EXT

EVNT7

EXT

EVNT6

EXT

EVNT5

EXT

EVNT4

EXT

EVNT3

EXT

EVNT2

EXT

EVNT1

MST

CMP4

MST

CMP3

MST

CMP2

MST

CMP1

MST

PER

CMP4 CMP2 UPDT

TIME

CMP1

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 TIMECPM2: Timer E compare 2

The timer F counter is reset upon timer E Compare 2 event.

Bit 30 TIMDCPM4: Timer D compare 4

The timer F counter is reset upon timer D compare 4 event.

Bit 29 TIMDCMP2: Timer D compare 2

The timer F counter is reset upon timer D compare 2 event.

Bit 28 TIMDCMP1: Timer D compare 1

The timer F counter is reset upon timer D compare 1 event.

Bit 27 TIMCCMP4: Timer C compare 4

The timer F counter is reset upon timer C compare 4 event.

Bit 26 TIMCCMP2: Timer C compare 2

The timer F counter is reset upon timer C compare 2 event.

Bit 25 TIMCCMP1: Timer C compare 1

The timer F counter is reset upon timer C compare 1 event.

Bit 24 TIMBCMP4: Timer B compare 4

The timer F counter is reset upon timer B compare 4 event.

Bit 23 TIMBCMP2: Timer B compare 2

The timer F counter is reset upon timer B compare 2 event.

Bit 22 TIMBCMP1: Timer B compare 1

The timer F counter is reset upon timer B compare 1 event.

Bit 21 TIMACMP4: Timer A compare 4

The timer F counter is reset upon timer A compare 4 event.

Bit 20 TIMACMP2: Timer A compare 2

The timer F counter is reset upon timer A compare 2 event.

Bit 19 TIMACMP1: Timer A compare 1

The timer F counter is reset upon timer A compare 1 event.

Bit 18

EXTEVNT10: External event

The timer F counter is reset upon external event 10.

Bit 17 EXTEVNT9: External event 9

The timer F counter is reset upon external event 9.

Loading...

Loading...