RM0440 Rev 4 1043/2126

RM0440 High-resolution timer (HRTIM)

1083

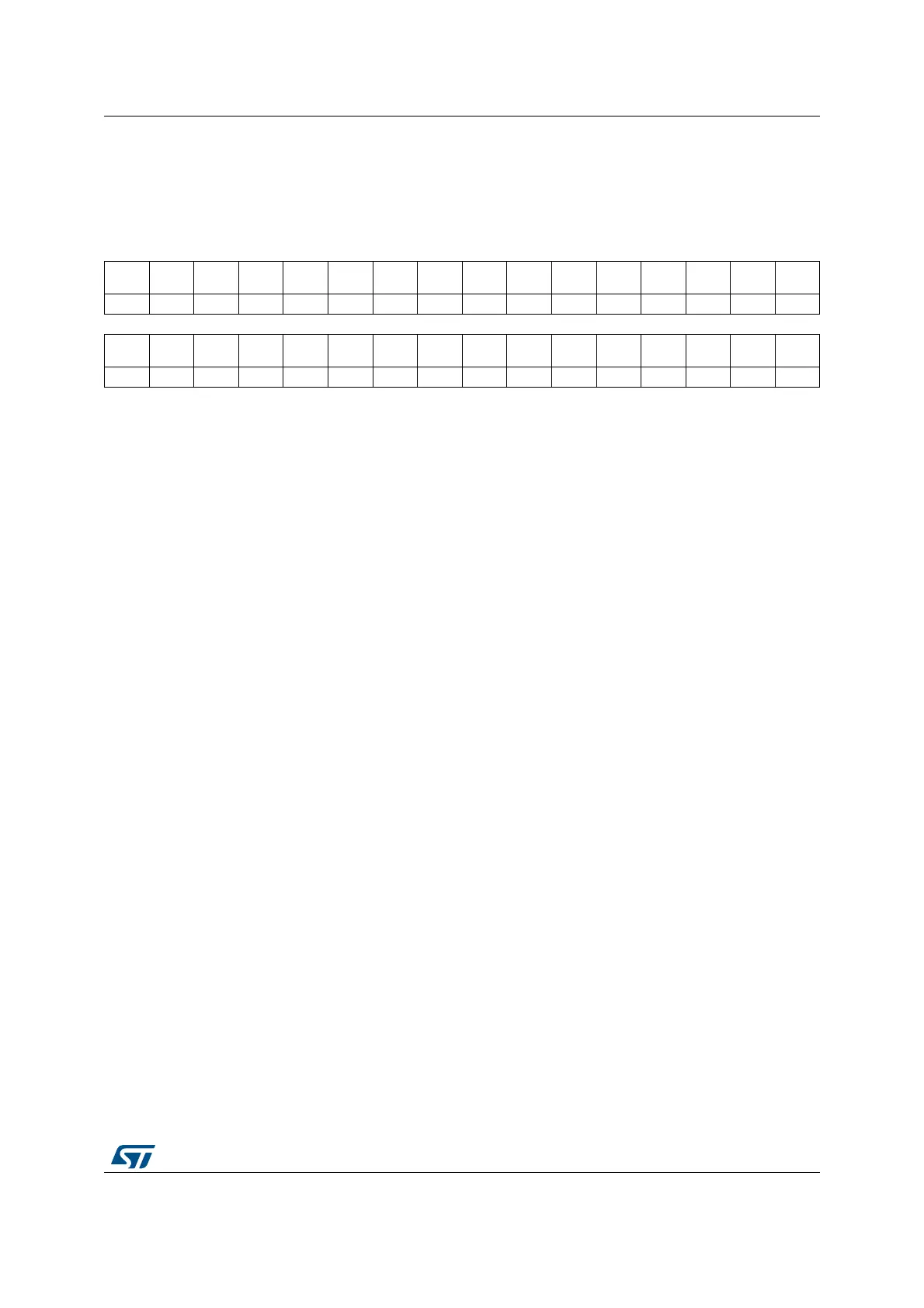

27.5.60 HRTIM burst mode trigger register (HRTIM_BMTRGR)

Address offset: 0x3A4

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OCHP

EV

EEV8 EEV7

TDEEV

8

TAEEV

7

TECMP

2

TECMP

1

TEREP

TF

CMP1

TDCM

P2

TF

REP

TDREP TDRST

TF

RST

TCCM

P1

TCREP

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

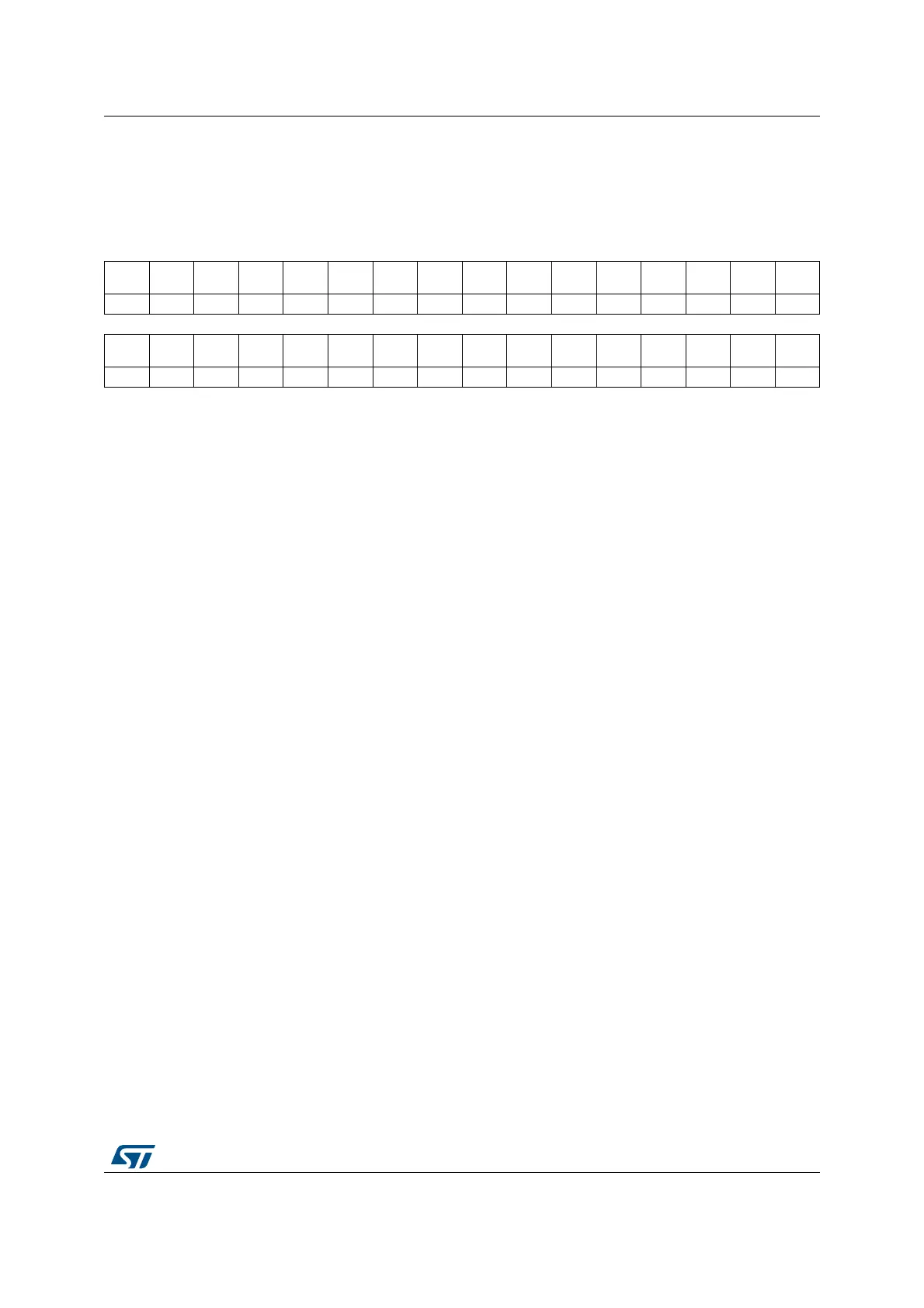

1514131211109876543210

TCRST

TBCMP

2

TBCMP

1

TBREP TBRST

TACMP

2

TACMP

1

TAREP TARST

MSTC

MP4

MSTC

MP3

MSTC

MP2

MSTC

MP1

MSTRE

P

MSTRS

T

SW

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 OCHPEV: On-chip event

A rising edge on the hrtim_bm_trg input (connected to general purpose timer TRGO output) triggers

a burst mode entry (see Table 207 for details).

Bit 30 EEV8: External event 8 (TIMD filters applied)

The external event 8 conditioned by TIMD filters is starting the burst mode operation.

Bit 29 EEV7: External event 7 (TIMA filters applied)

The external event 7 conditioned by TIMA filters is starting the burst mode operation.

Bit 28 TDEEV8: Timer D period following external event 8

The timer D period following an external event 8 (conditioned by TIMD filters) is starting the burst

mode operation.

Bit 27 TAEEV7: Timer A period following external event 7

The timer A period following an external event 7 (conditioned by TIMA filters) is starting the burst

mode operation.

Bit 26 TECMP2: Timer E compare 2 event

Refer to TACMP1 description.

Bit 25 TECMP1: Timer E compare 1 event

Refer to TACMP1 description.

Bit 24 TEREP: Timer E repetition

Refer to TAREP description.

Bit 23 TFCMP1: Timer F compare 1 event

Refer to TACMP1 description.

Bit 22 TDCMP2: Timer D compare 2 event

Refer to TACMP1 description.

Bit 21 TFREP: Timer F repetition

Refer to TAREP description.

Bit 20 TDREP: Timer D repetition

Refer to TAREP description.

Bit 19 TDRST: Timer D reset or roll-over

Refer to TARST description.

Bit 18 TFRST: Timer F reset

Refer to TARST description.

Loading...

Loading...