General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0440

1314/2126 RM0440 Rev 4

29.5.5 TIMx status register (TIMx_SR)(x = 2 to 5)

Address offset: 0x010

Reset value: 0x0000 0000

Bit 7 Reserved, must be kept at reset value.

Bit 6 TIE: Trigger interrupt enable

0: Trigger interrupt disabled.

1: Trigger interrupt enabled.

Bit 5 Reserved, must be kept at reset value.

Bit 4 CC4IE: Capture/Compare 4 interrupt enable

0: CC4 interrupt disabled.

1: CC4 interrupt enabled.

Bit 3 CC3IE: Capture/Compare 3 interrupt enable

0: CC3 interrupt disabled.

1: CC3 interrupt enabled.

Bit 2 CC2IE: Capture/Compare 2 interrupt enable

0: CC2 interrupt disabled.

1: CC2 interrupt enabled.

Bit 1 CC1IE: Capture/Compare 1 interrupt enable

0: CC1 interrupt disabled.

1: CC1 interrupt enabled.

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled.

1: Update interrupt enabled.

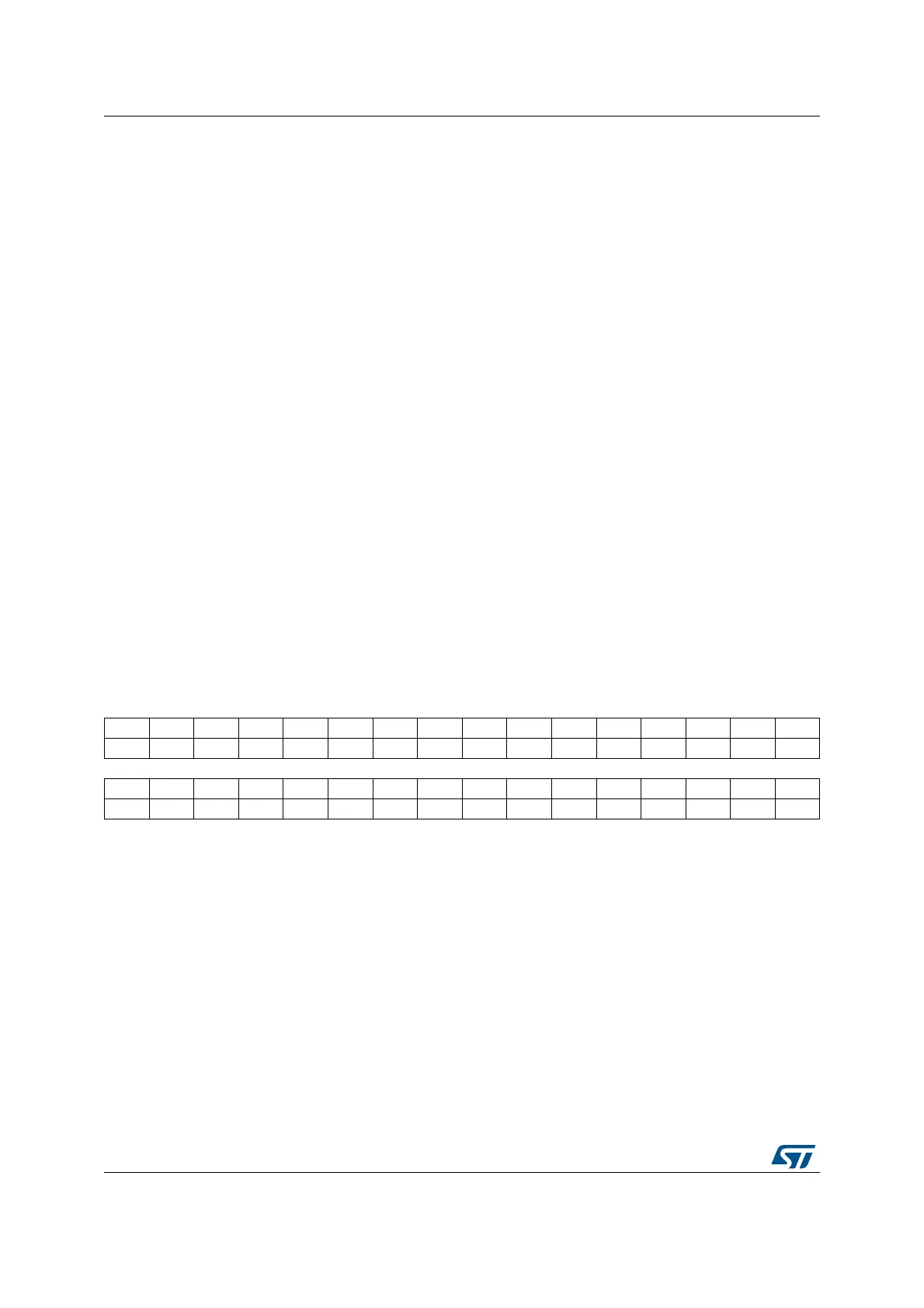

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. TERRF IERRF DIRF IDXF Res. Res. Res. Res.

rc_w0 rc_w0 rc_w0 rc_w0

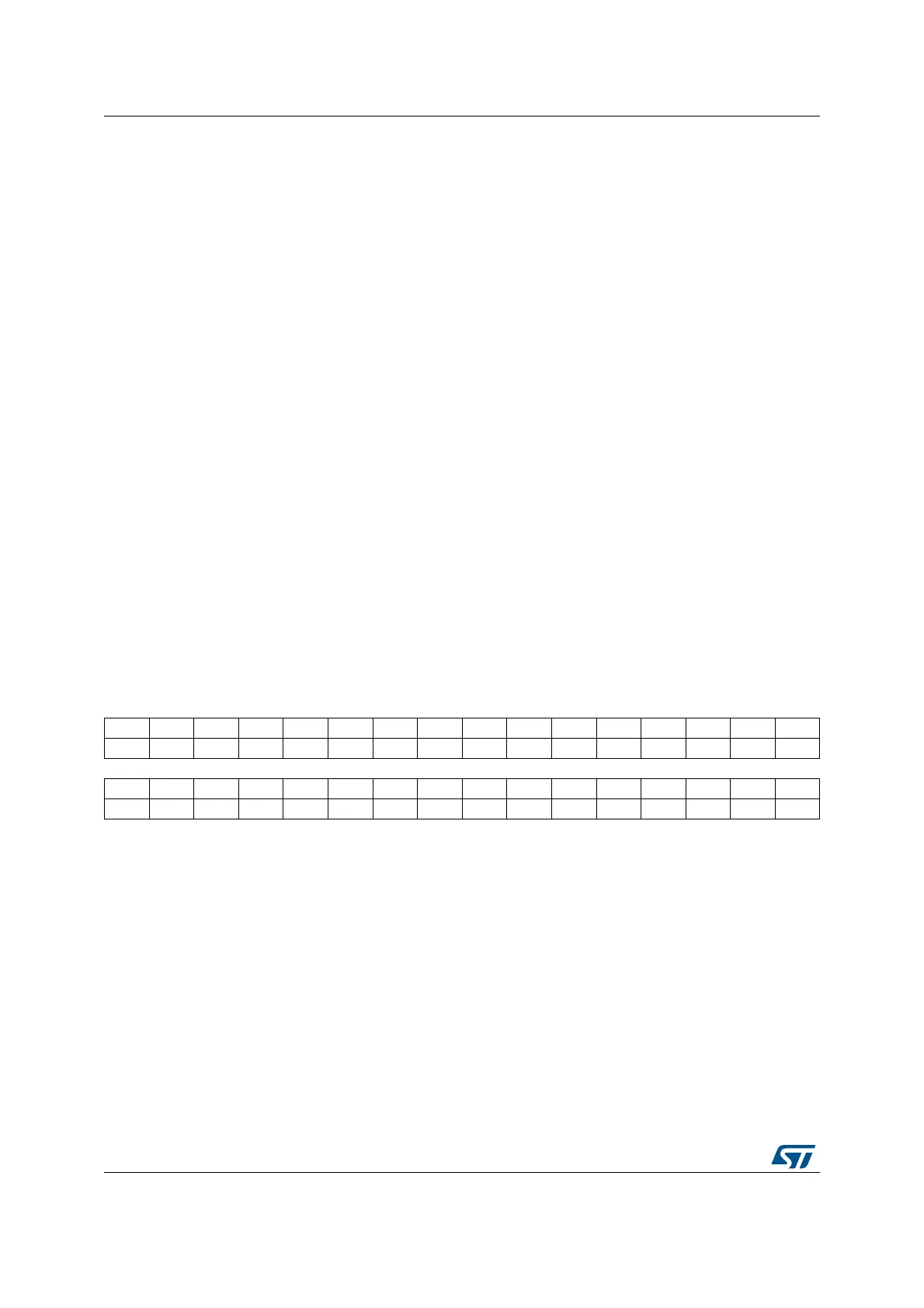

1514131211109876543210

Res. Res. Res. CC4OF CC3OF CC2OF CC1OF Res. Res. TIF Res. CC4IF CC3IF CC2IF CC1IF UIF

rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0 rc_w0

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 TERRF: Transition error interrupt flag

This flag is set by hardware when a transition error is detected in encoder mode. It is cleared

by software by writing it to ‘0’.

0: No encoder transition error has been detected.

1: An encoder transition error has been detected

Bit 22 IERRF: Index error interrupt flag

This flag is set by hardware when an index error is detected. It is cleared by software by

writing it to ‘0’.

0: No index error has been detected.

1: An index error has been detected

Loading...

Loading...