RM0440 Rev 4 1401/2126

RM0440 General-purpose timers (TIM15/TIM16/TIM17)

1445

30.7.8 TIM15 capture/compare mode register 1 [alternate]

(TIM15_CCMR1)

Address offset: 0x18

Reset value: 0x0000 0000

The same register can be used for output compare mode (this section) or for input capture

mode (previous section). The direction of a channel is defined by configuring the

corresponding CCxS bits. All the other bits of this register have a different function for input

capture and for output compare modes. It is possible to combine both modes independently

(e.g. channel 1 in input capture mode and channel 2 in output compare mode).

T

Output compare mode:

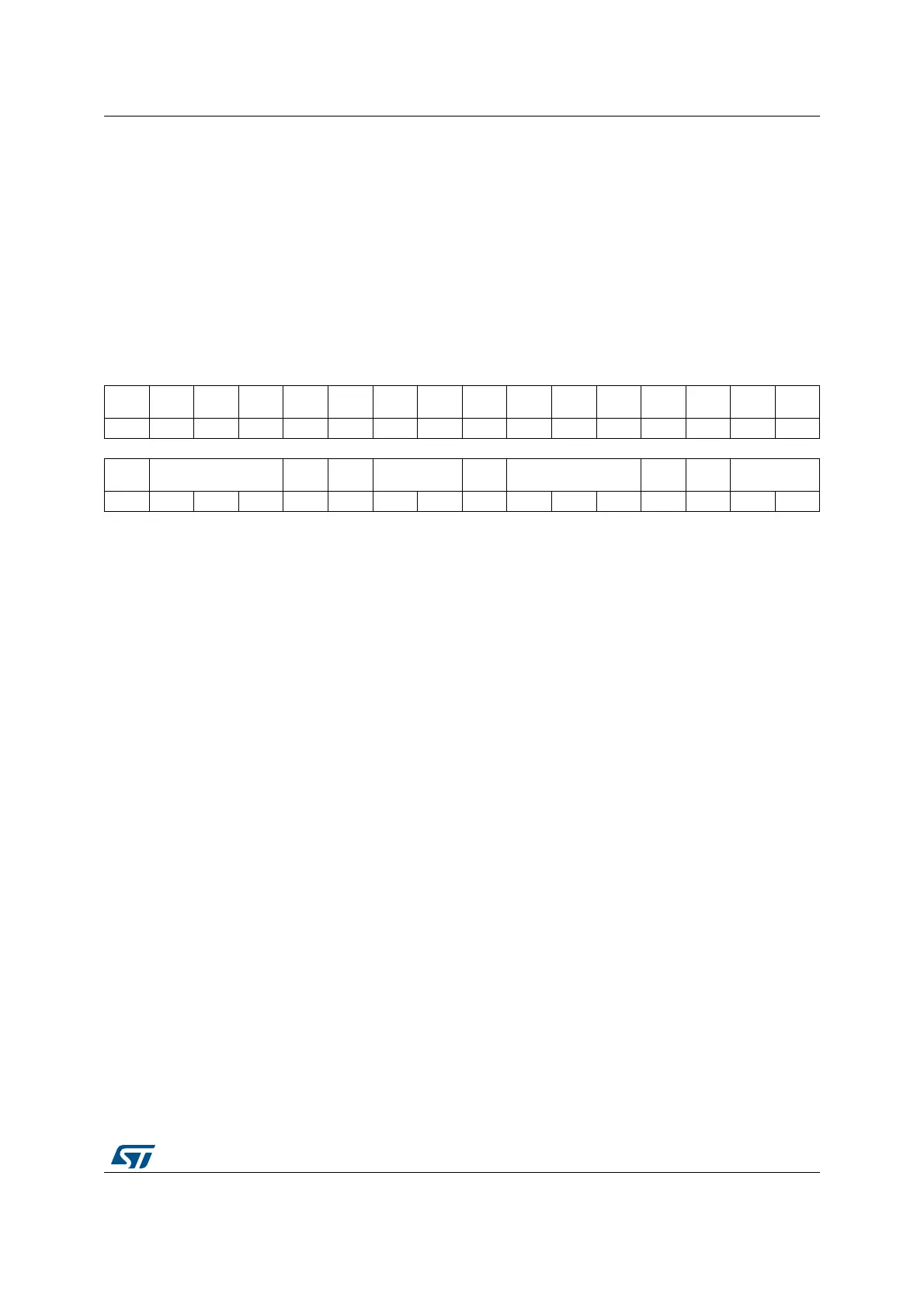

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res.

OC2M

[3]

Res. Res. Res. Res. Res. Res. Res.

OC1M

[3]

rw rw

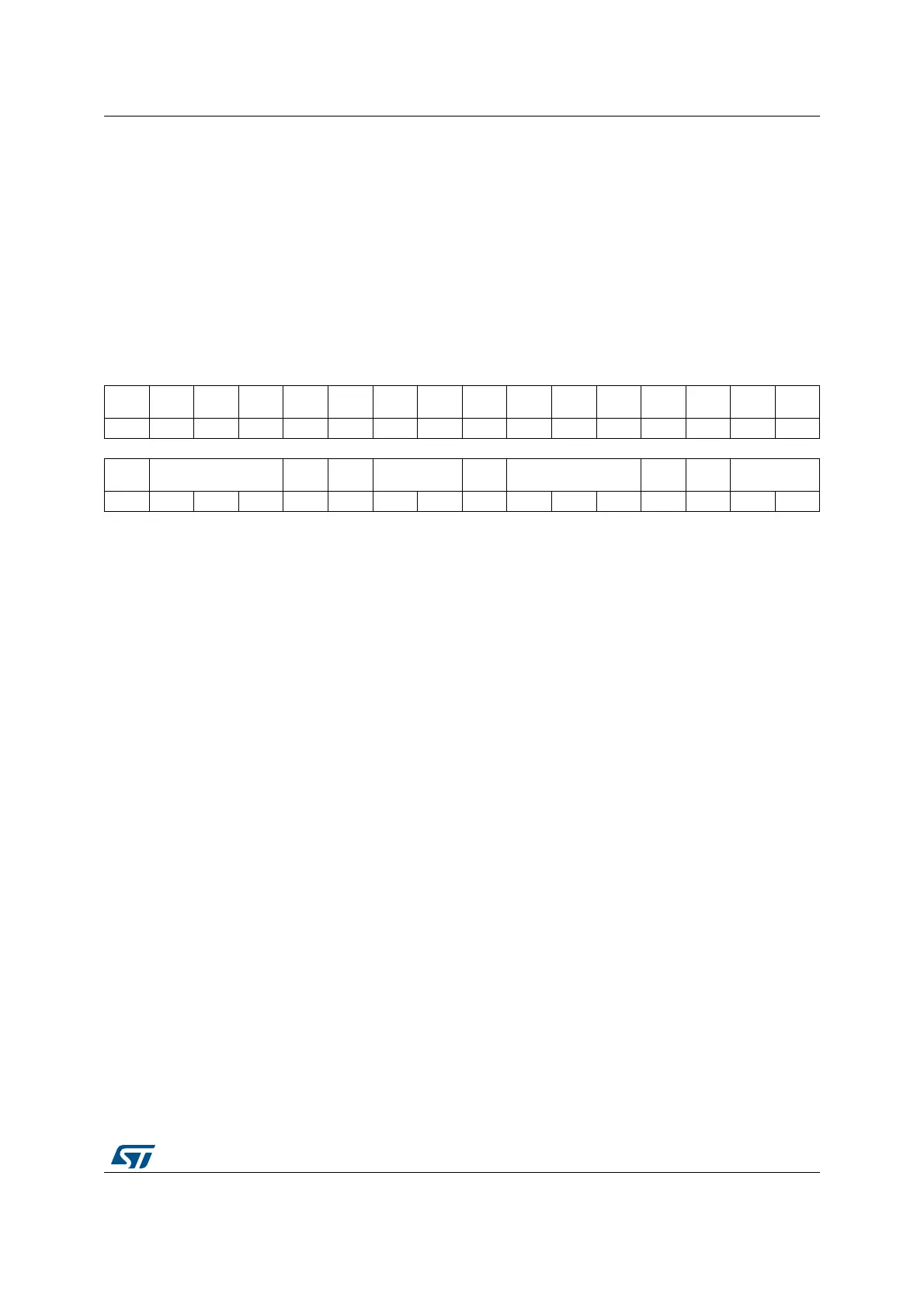

1514131211109876543210

OC2

CE

OC2M[2:0]

OC2

PE

OC2

FE

CC2S[1:0]

OC1

CE

OC1M[2:0]

OC1

PE

OC1

FE

CC1S[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:25 Reserved, must be kept at reset value.

Bits 23:17 Reserved, must be kept at reset value.

Bit 15 OC2CE: Output compare 2 clear enable

Bits 24, 14:12 OC2M[3:0]: Output compare 2 mode

Bit 11 OC2PE: Output compare 2 preload enable

Bit 10 OC2FE: Output compare 2 fast enable

Bits 9:8 CC2S[1:0]: Capture/Compare 2 selection

This bit-field defines the direction of the channel (input/output) as well as the used input.

00: CC2 channel is configured as output.

01: CC2 channel is configured as input, tim_ic2 is mapped on tim_ti2.

10: C2 channel is configured as input, tim_ic2 is mapped on tim_ti1.

11: CC2 channel is configured as input, tim_ic2 is mapped on tim_trc. This mode is working

only if an internal trigger input is selected through the TS bit (TIM15_SMCR register)

Note: CC2S bits are writable only when the channel is OFF (CC2E = ‘0’ in TIM15_CCER).

Bit 7 OC1CE: Output compare 1 clear enable

0: tim_oc1ref is not affected by the tim_ocref_clr_int input.

1: tim_oc1ref is cleared as soon as a High level is detected on tim_ocref_clr_int input.

Loading...

Loading...