Low-power timer (LPTIM) RM0440

1480/2126 RM0440 Rev 4

Caution: The LPTIM_IER register must only be modified when the LPTIM is disabled (ENABLE bit reset to ‘0’)

32.7.4 LPTIM configuration register (LPTIM_CFGR)

Address offset: 0x00C

Reset value: 0x0000 0000

Bits 31:9 Reserved, must be kept at reset value.

Bits 8:7 Reserved, must be kept at reset value.

Bit 6 DOWNIE: Direction change to down Interrupt Enable

0: DOWN interrupt disabled

1: DOWN interrupt enabled

Note: If the LPTIM does not support encoder mode feature, this bit is reserved. Please refer to

Section 32.3: LPTIM implementation.

Bit 5 UPIE: Direction change to UP Interrupt Enable

0: UP interrupt disabled

1: UP interrupt enabled

Note: If the LPTIM does not support encoder mode feature, this bit is reserved. Please refer to

Section 32.3: LPTIM implementation.

Bit 4 ARROKIE: Autoreload register update OK Interrupt Enable

0: ARROK interrupt disabled

1: ARROK interrupt enabled

Bit 3 CMPOKIE: Compare register update OK Interrupt Enable

0: CMPOK interrupt disabled

1: CMPOK interrupt enabled

Bit 2 EXTTRIGIE: External trigger valid edge Interrupt Enable

0: EXTTRIG interrupt disabled

1: EXTTRIG interrupt enabled

Bit 1 ARRMIE: Autoreload match Interrupt Enable

0: ARRM interrupt disabled

1: ARRM interrupt enabled

Bit 0 CMPMIE: Compare match Interrupt Enable

0: CMPM interrupt disabled

1: CMPM interrupt enabled

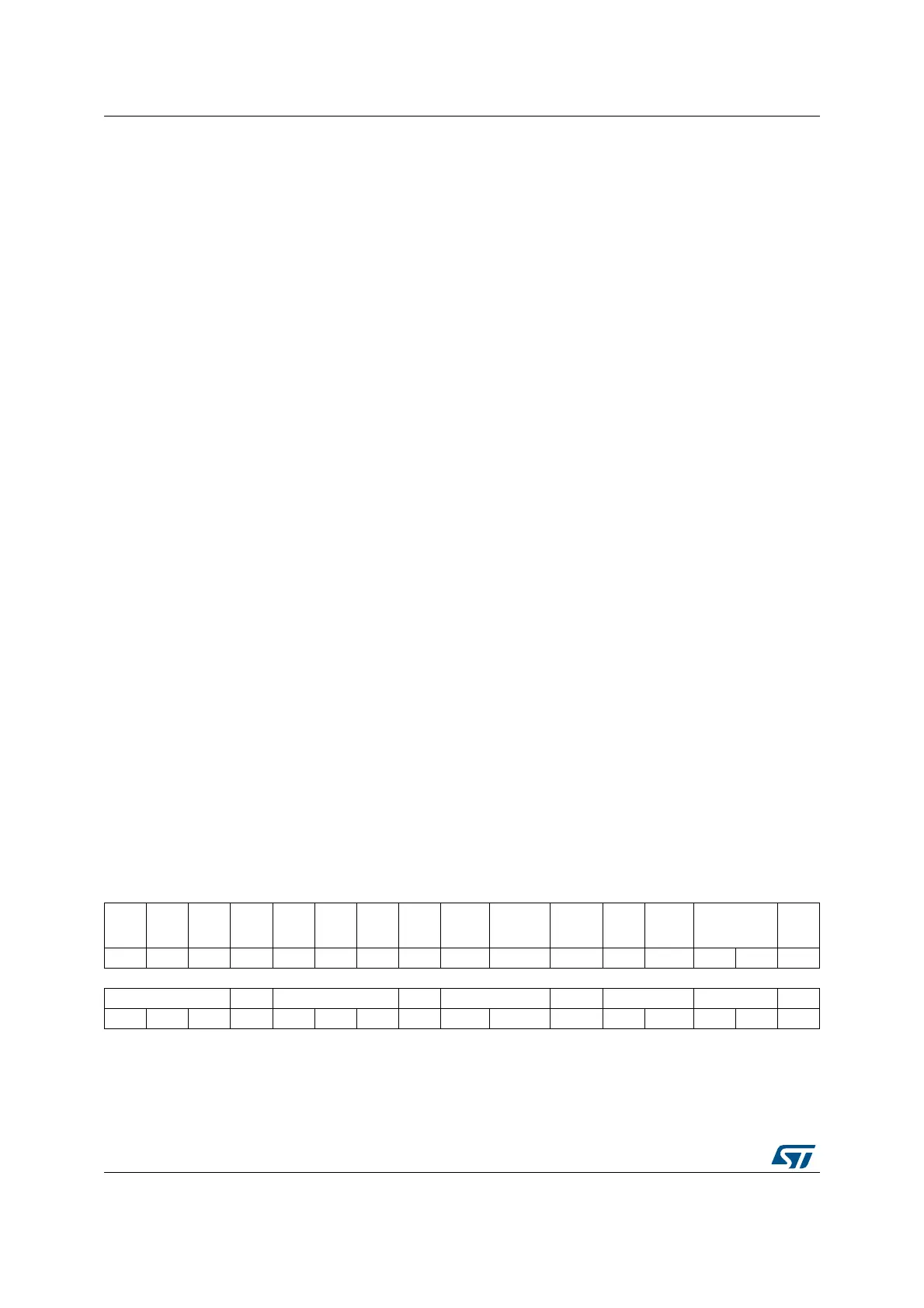

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res.

TRIG

SEL

[3]

Res. Res. Res. Res. ENC

COUNT

MODE

PRELOAD WAVPOL WAVE TIMOUT TRIGEN[1:0] Res.

rw rw rw rw rw rw rw rw rw

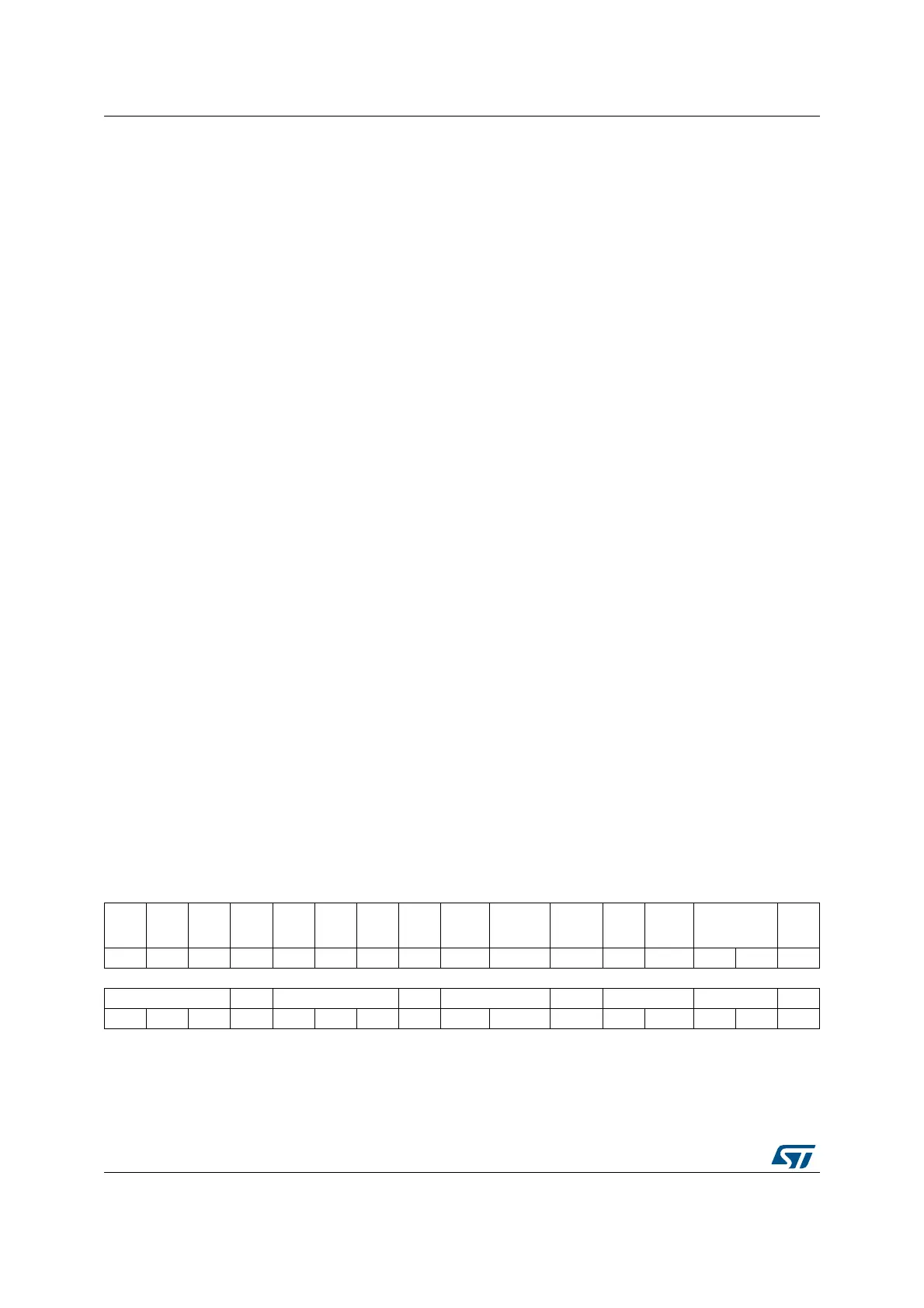

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRIGSEL[2:0] Res. PRESC[2:0] Res. TRGFLT[1:0] Res. CKFLT[1:0] CKPOL[1:0] CKSEL

rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...