Real-time clock (RTC) RM0440

1574/2126 RM0440 Rev 4

35.6.20 RTC status clear register (RTC_SCR)

Address offset: 0x5C

Backup domain reset value: 0x0000 0000

System reset: not affected

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 ITSMF: Internal timestamp masked flag

This flag is set by hardware when a timestamp on the internal event occurs and

timestampinterrupt is raised.

Bit 4 TSOVMF: Timestamp overflow masked flag

This flag is set by hardware when a timestamp interrupt occurs while TSMF is already set.

It is recommended to check and then clear TSOVF only after clearing the TSF bit. Otherwise,

an overflow might not be noticed if a timestamp event occurs immediately before the TSF bit

is cleared.

Bit 3 TSMF: Timestamp masked flag

This flag is set by hardware when a timestamp interrupt occurs.

If ITSF flag is set, TSF must be cleared together with ITSF.

Bit 2 WUTMF: Wakeup timer masked flag

This flag is set by hardware when the wakeup timer interrupt occurs.

This flag must be cleared by software at least 1.5 RTCCLK periods before WUTF is set to 1

again.

Bit 1 ALRBMF: Alarm B masked flag

This flag is set by hardware when the alarm B interrupt occurs.

Bit 0 ALRAMF: Alarm A masked flag

This flag is set by hardware when the alarm A interrupt occurs.

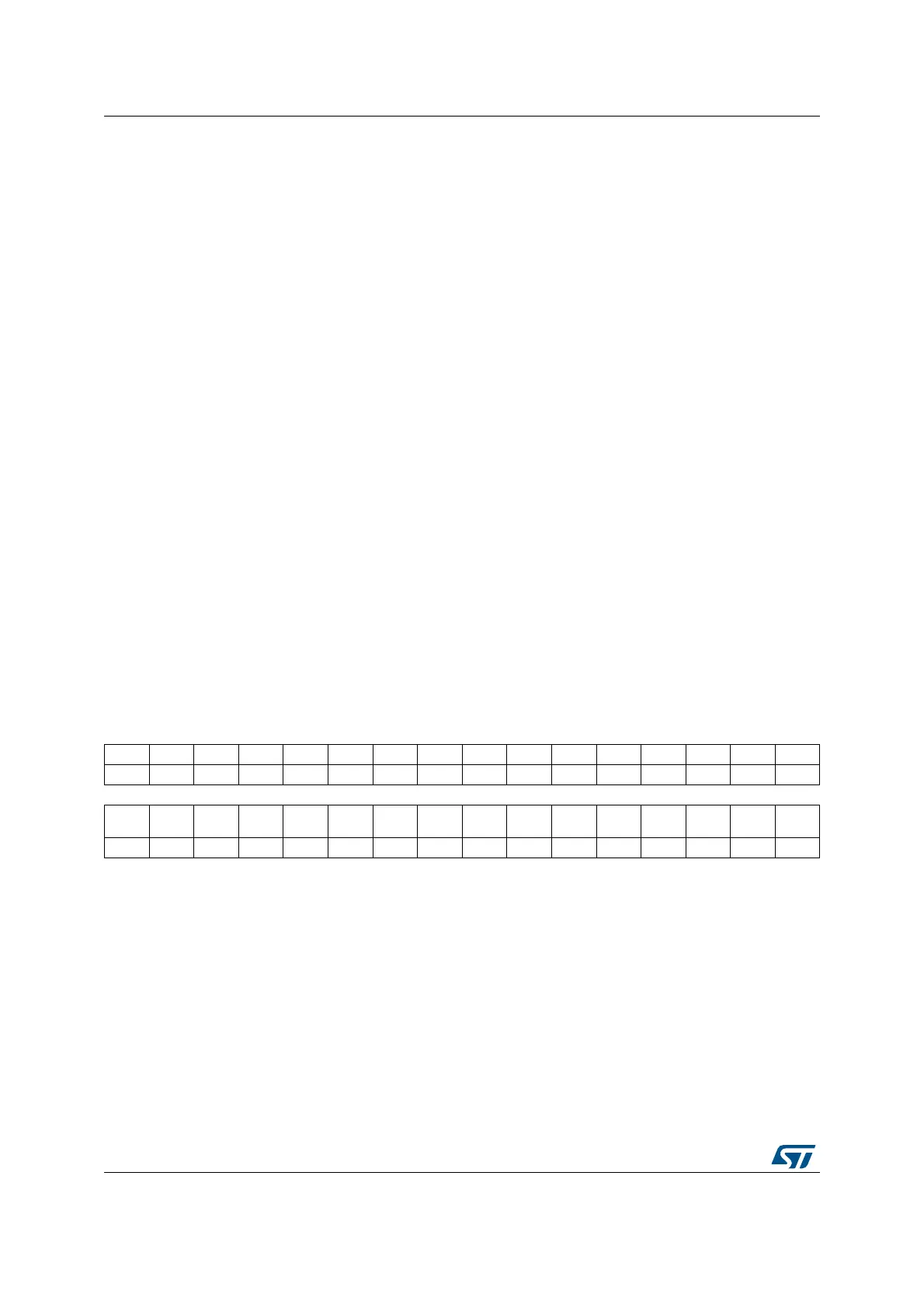

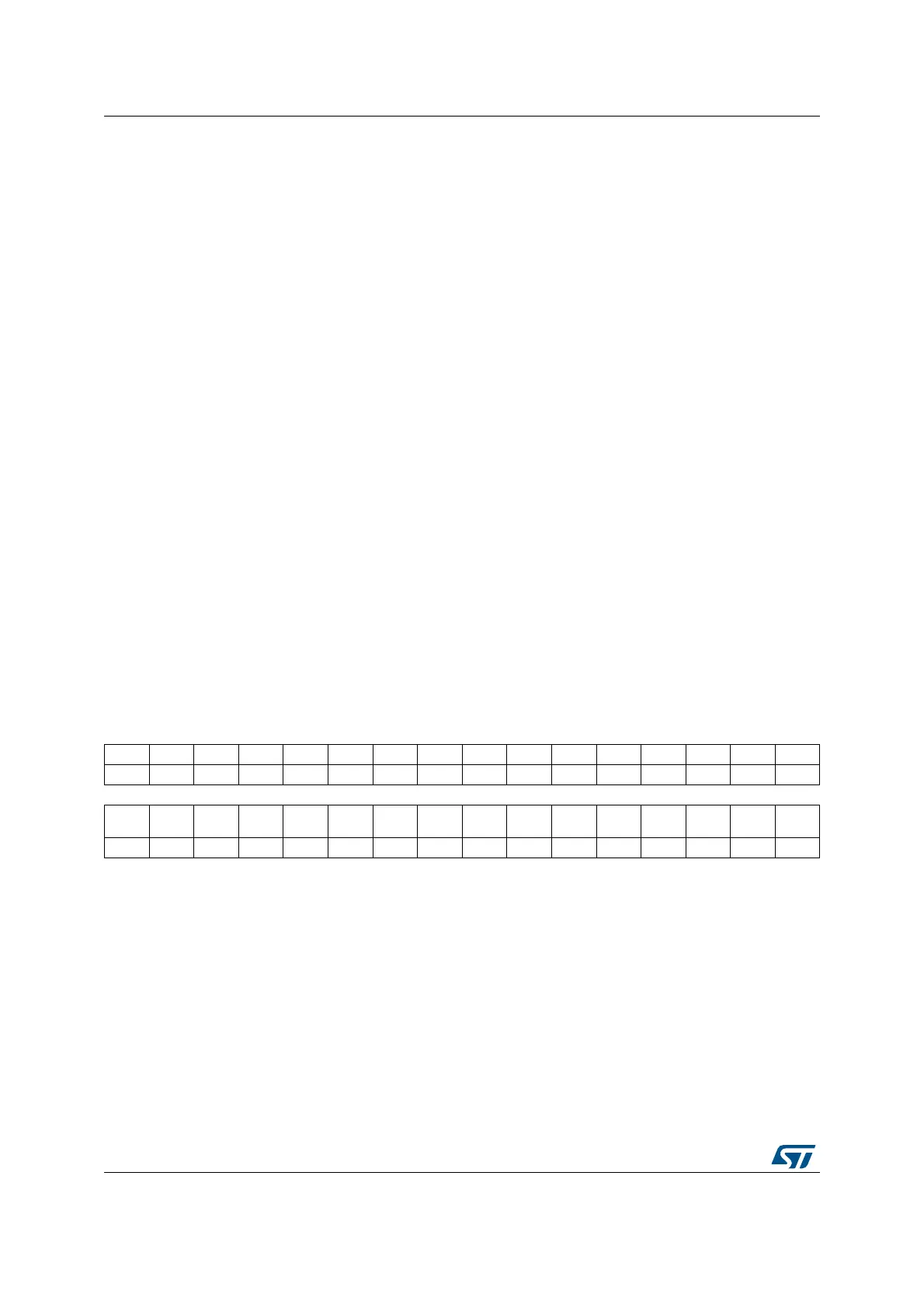

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

CITS

F

CTSOV

F

CTS

F

CWUT

F

CALRB

F

CALRA

F

wwwwww

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 CITSF: Clear internal timestamp flag

Writing 1 in this bit clears the ITSF bit in the RTC_SR register.

Bit 4 CTSOVF: Clear timestamp overflow flag

Writing 1 in this bit clears the TSOVF bit in the RTC_SR register.

It is recommended to check and then clear TSOVF only after clearing the TSF bit. Otherwise,

an overflow might not be noticed if a timestamp event occurs immediately before the TSF bit

is cleared.

Bit 3 CTSF: Clear timestamp flag

Writing 1 in this bit clears the TSOVF bit in the RTC_SR register.

If ITSF flag is set, TSF must be cleared together with ITSF by setting CRSF and CITSF.

Loading...

Loading...