Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0440

1644/2126 RM0440 Rev 4

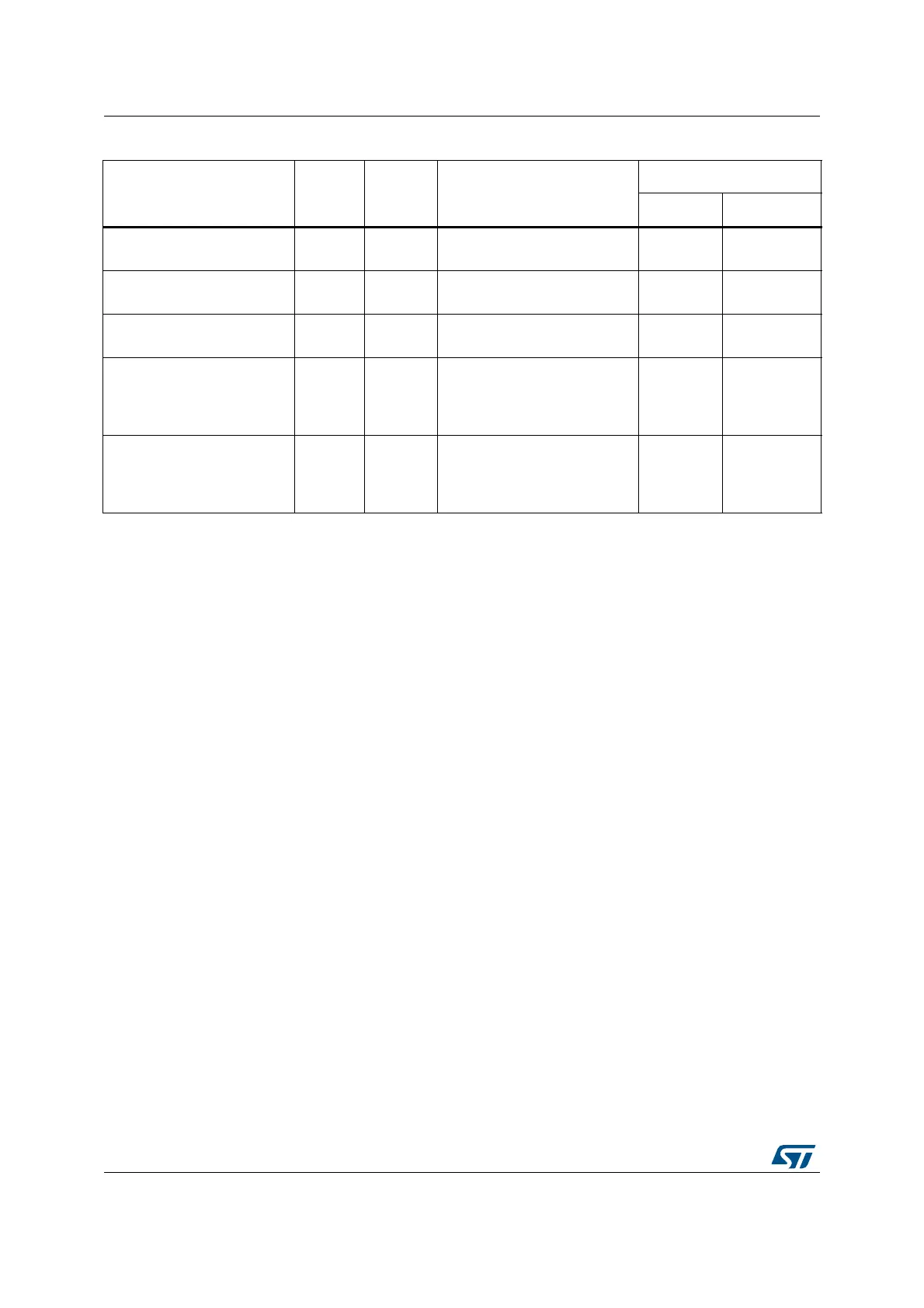

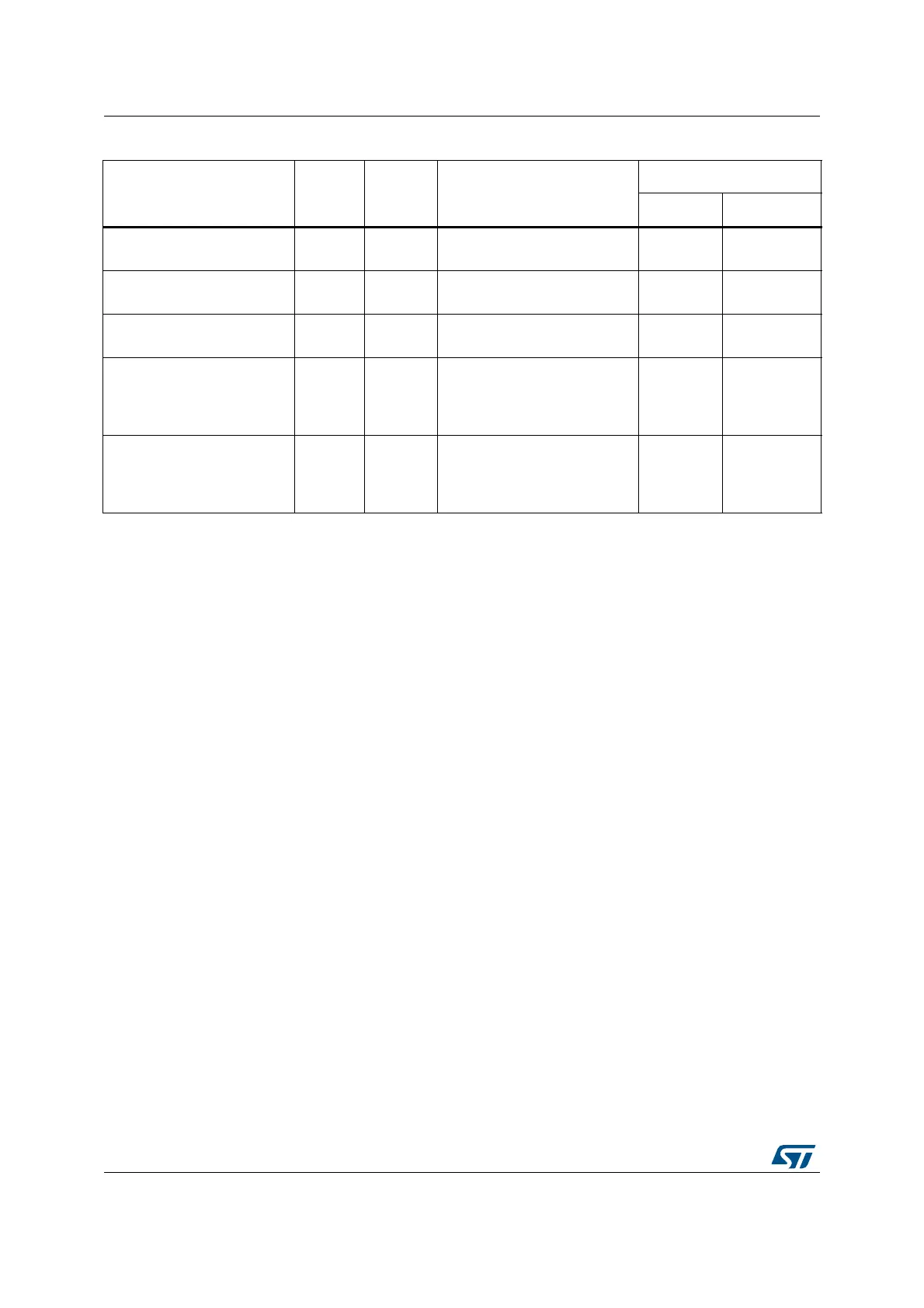

End of Block EOBF EOBIE

EOBF is cleared by setting

EOBCF bit.

YES NO

Wakeup from low-power

mode

WUF WUFIE

WUF is cleared by setting

WUCF bit.

YES YES

SPI slave underrun error UDR EIE

UDR is cleared by setting

UDRCF bit.

YES NO

Transmit FIFO threshold

reached

TXFT TXFTIE

TXFT is cleared by hardware

when the TXFIFO content is

less than the programmed

threshold

YES YES

Receive FIFO threshold

reached

RXFT RXFTIE

RXFT is cleared by hardware

when the RXFIFO content is

less than the programmed

threshold.

YES YES

1. RXFF flag is asserted if the USART receives n+1 data (n being the RXFIFO size): n data in the RXFIFO and 1 data in

USART_RDR. In Stop mode, USART_RDR is not clocked. As a result, this register is not written and once n data are

received and written in the RXFIFO, the RXFF interrupt is asserted (RXFF flag is not set).

Table 348. USART interrupt requests (continued)

Interrupt event

Event

flag

Enable

Control

bit

Interrupt clear method

Interrupt activated

usart_it usart_wkup

Loading...

Loading...