Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0440

1652/2126 RM0440 Rev 4

37.7.3 USART control register 2 (USART_CR2)

Address offset: 0x04

Reset value: 0x0000 0000

Bit 2 RE: Receiver enable

This bit enables the receiver. It is set and cleared by software.

0: Receiver is disabled

1: Receiver is enabled and begins searching for a start bit

Bit 1 UESM: USART enable in low-power mode

When this bit is cleared, the USART cannot wake up the MCU from low-power mode.

When this bit is set, the USART can wake up the MCU from low-power mode.

This bit is set and cleared by software.

0: USART not able to wake up the MCU from low-power mode.

1: USART able to wake up the MCU from low-power mode.

Note: It is recommended to set the UESM bit just before entering low-power mode and clear it

when exit from low-power mode.

If the USART does not support the wakeup from Stop feature, this bit is reserved and

must be kept at reset value. Refer to Section 37.4: USART implementation on

page 1595.

Bit 0 UE: USART enable

When this bit is cleared, the USART prescalers and outputs are stopped immediately, and all

current operations are discarded. The USART configuration is kept, but all the USART_ISR

status flags are reset. This bit is set and cleared by software.

0: USART prescaler and outputs disabled, low-power mode

1: USART enabled

Note: To enter low-power mode without generating errors on the line, the TE bit must be

previously reset and the software must wait for the TC bit in the USART_ISR to be set

before resetting the UE bit.

The DMA requests are also reset when UE = 0 so the DMA channel must be disabled

before resetting the UE bit.

In Smartcard mode, (SCEN = 1), the SCLK is always available when CLKEN = 1,

regardless of the UE bit value.

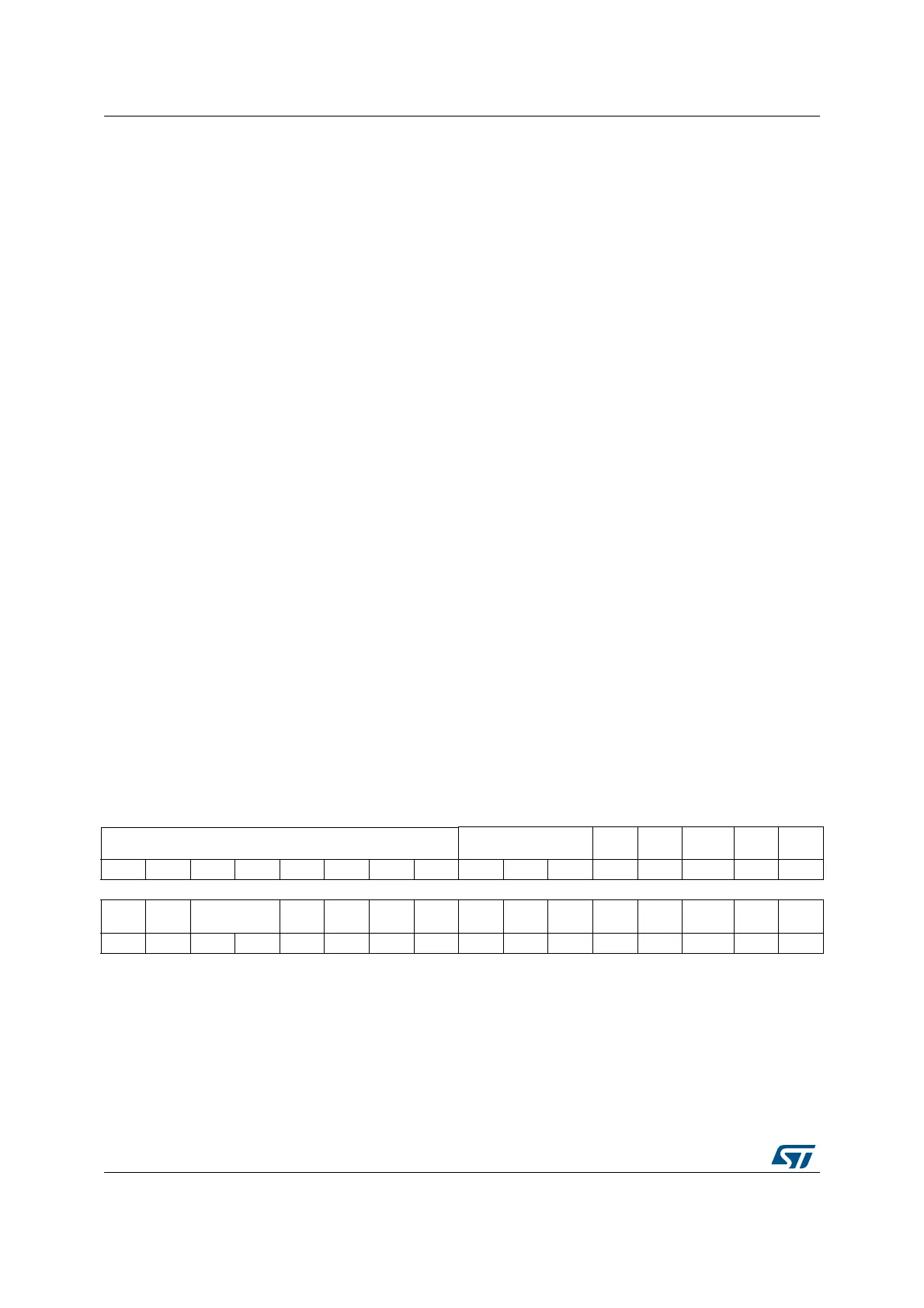

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ADD[7:0] RTOEN ABRMOD[1:0] ABREN

MSBFI

RST

DATAINV TXINV RXINV

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

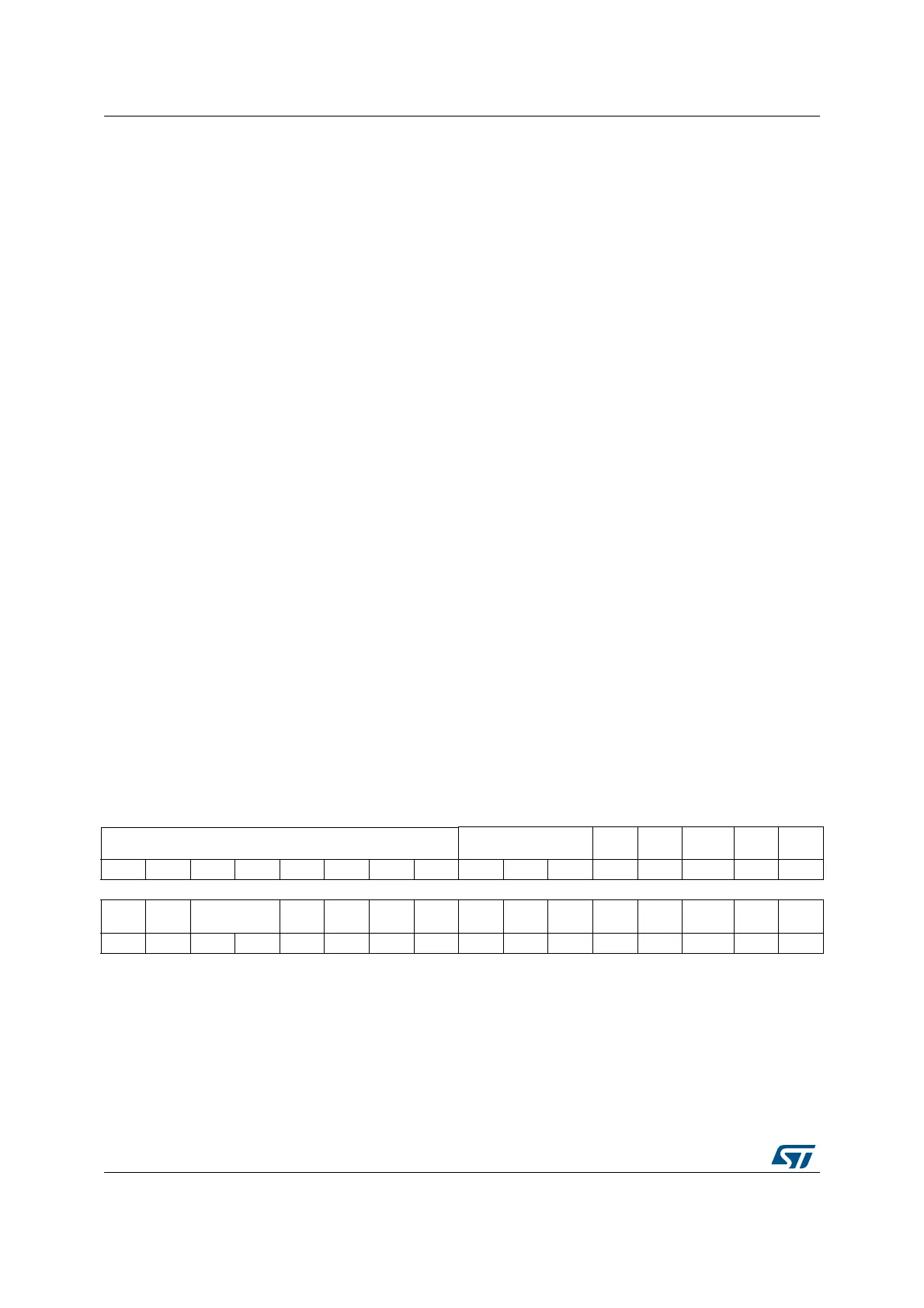

1514131211109876543 2 10

SWAP LINEN STOP[1:0] CLKEN CPOL CPHA LBCL Res. LBDIE LBDL ADDM7

DIS_

NSS

Res. Res. SLVEN

rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...