Universal synchronous/asynchronous receiver transmitter (USART/UART) RM0440

1656/2126 RM0440 Rev 4

Note: The CPOL, CPHA and LBCL bits should not be written while the transmitter is enabled.

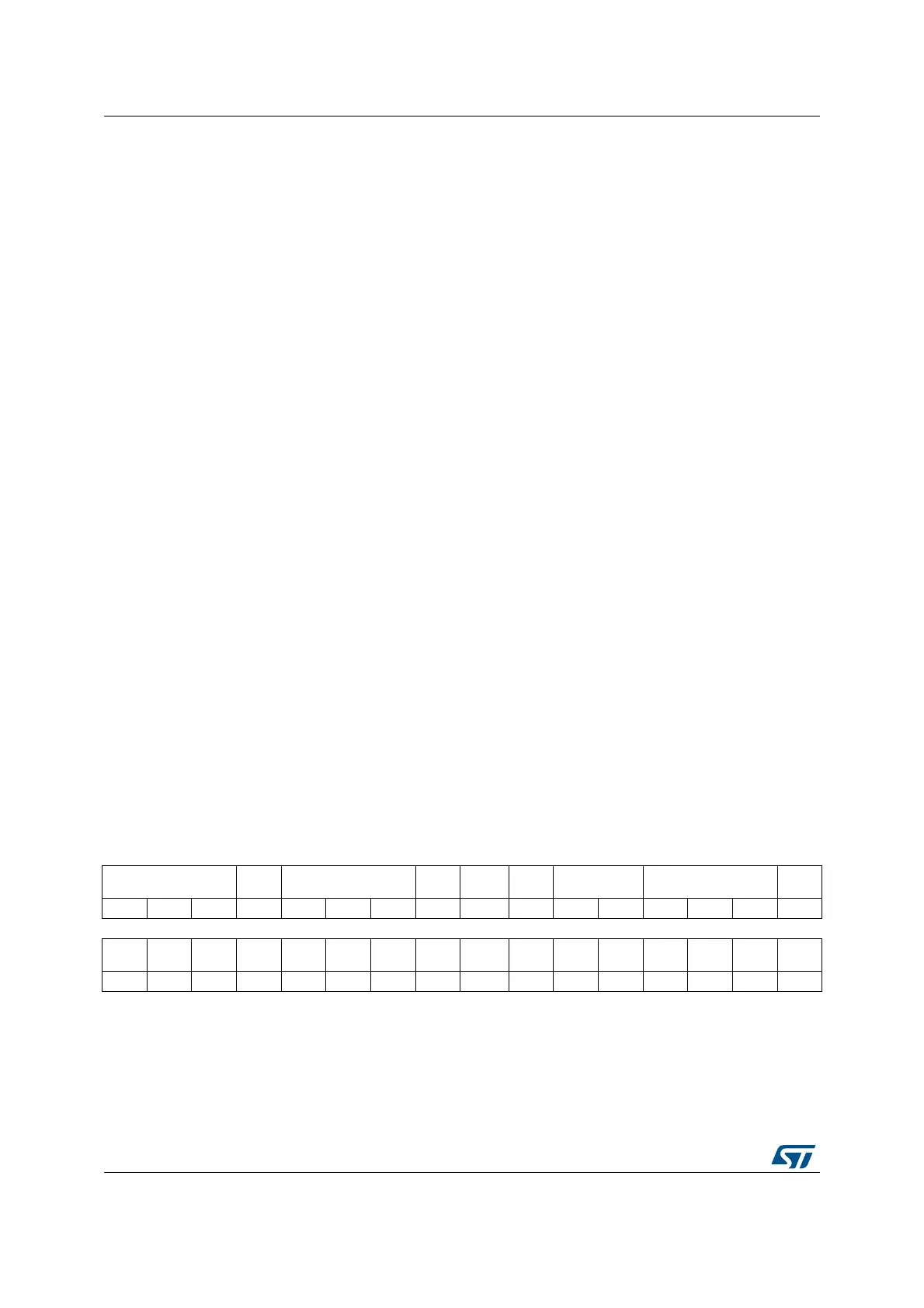

37.7.4 USART control register 3 (USART_CR3)

Address offset: 0x08

Reset value: 0x0000 0000

Bit 5 LBDL: LIN break detection length

This bit is for selection between 11 bit or 10 bit break detection.

0: 10-bit break detection

1: 11-bit break detection

This bit can only be written when the USART is disabled (UE=0).

Note: If LIN mode is not supported, this bit is reserved and must be kept at reset value. Refer to

Section 37.4: USART implementation on page 1595.

Bit 4 ADDM7: 7-bit Address Detection/4-bit Address Detection

This bit is for selection between 4-bit address detection or 7-bit address detection.

0: 4-bit address detection

1: 7-bit address detection (in 8-bit data mode)

This bit can only be written when the USART is disabled (UE=0)

Note: In 7-bit and 9-bit data modes, the address detection is done on 6-bit and 8-bit address

(ADD[5:0] and ADD[7:0]) respectively.

Bit 3 DIS_NSS:

When the DIS_NSS bit is set, the NSS pin input is ignored.

0: SPI slave selection depends on NSS input pin.

1: SPI slave is always selected and NSS input pin is ignored.

Note: When SPI slave mode is not supported, this bit is reserved and must be kept at reset value.

Refer to Section 37.4: USART implementation on page 1595.

Bits 2:1 Reserved, must be kept at reset value.

Bit 0 SLVEN: Synchronous Slave mode enable

When the SLVEN bit is set, the synchronous slave mode is enabled.

0: Slave mode disabled.

1: Slave mode enabled.

Note: When SPI slave mode is not supported, this bit is reserved and must be kept at reset value.

Refer to Section 37.4: USART implementation on page 1595.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TXFTCFG[2:0]

RXF

TIE

RXFTCFG[2:0]

TCBG

TIE

TXFTIE WUFIE WUS[1:0] SCARCNT[2:0] Res.

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15141312111098 7 6543210

DEP DEM DDRE

OVR

DIS

ONE

BIT

CTSIE CTSE RTSE DMAT DMAR SCEN NACK

HD

SEL

IRLP IREN EIE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...