Serial peripheral interface / integrated interchip sound (SPI/I2S) RM0440

1786/2126 RM0440 Rev 4

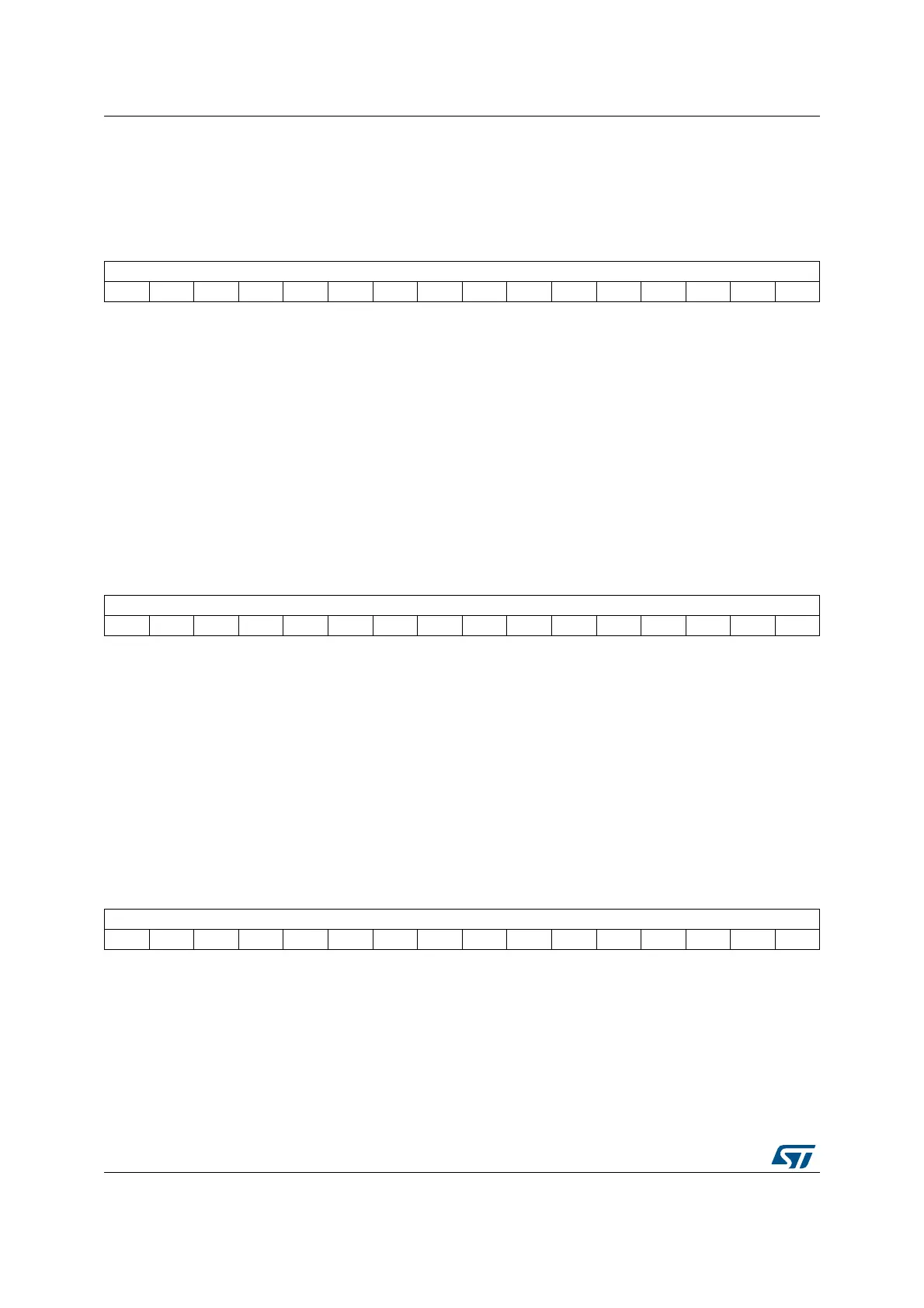

39.9.4 SPI data register (SPIx_DR)

Address offset: 0x0C

Reset value: 0x0000

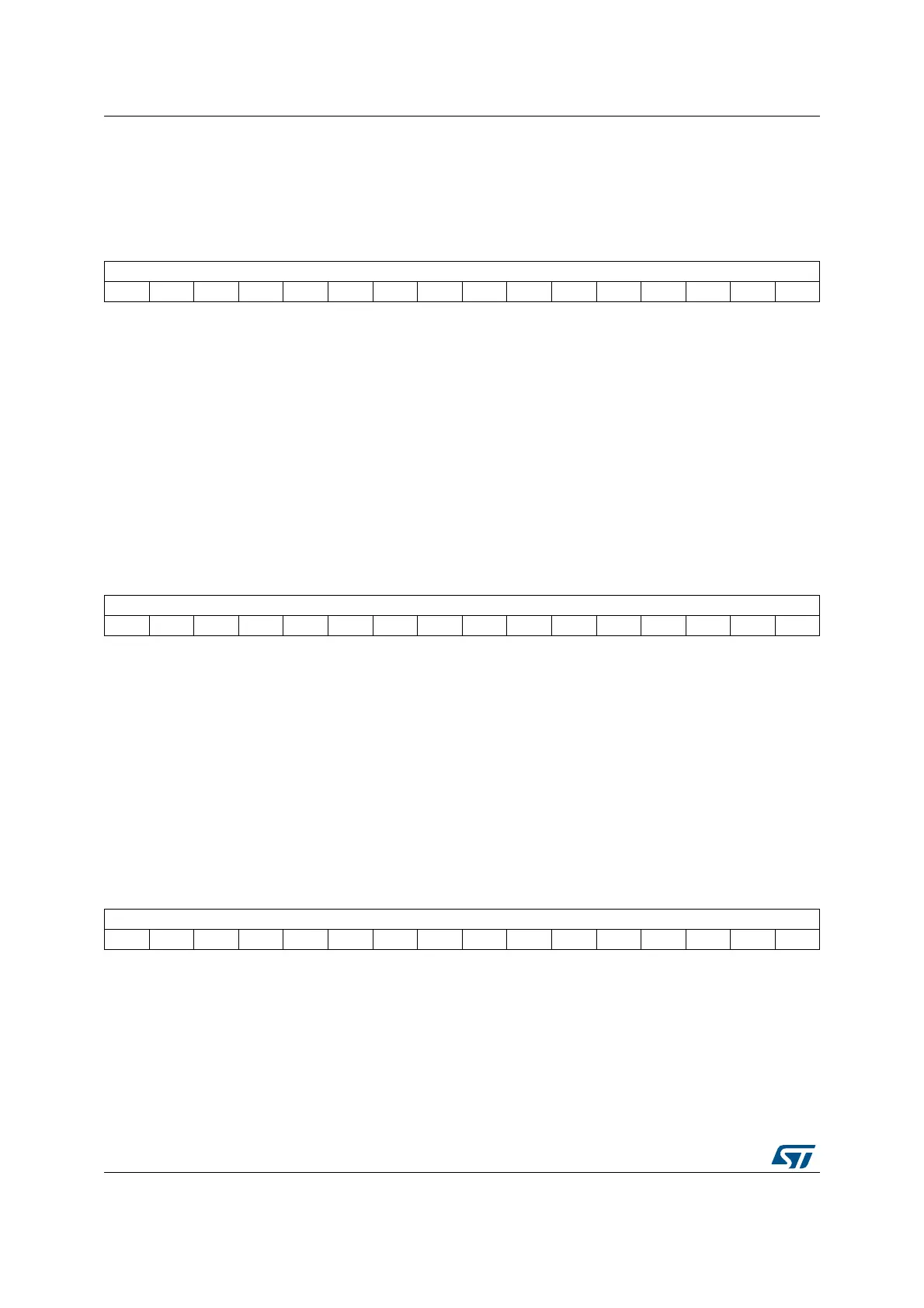

39.9.5 SPI CRC polynomial register (SPIx_CRCPR)

Address offset: 0x10

Reset value: 0x0007

Note: The polynomial value should be odd only. No even value is supported.

39.9.6 SPI Rx CRC register (SPIx_RXCRCR)

Address offset: 0x14

Reset value: 0x0000

1514131211109876543210

DR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 DR[15:0]: Data register

Data received or to be transmitted

The data register serves as an interface between the Rx and Tx FIFOs. When the data

register is read, RxFIFO is accessed while the write to data register accesses TxFIFO (See

Section 39.5.9: Data transmission and reception procedures).

Note: Data is always right-aligned. Unused bits are ignored when writing to the register, and

read as zero when the register is read. The Rx threshold setting must always

correspond with the read access currently used.

1514131211109876543210

CRCPOLY[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0 CRCPOLY[15:0]: CRC polynomial register

This register contains the polynomial for the CRC calculation.

The CRC polynomial (0x0007) is the reset value of this register. Another polynomial can be

configured as required.

1514131211109876543210

RXCRC[15:0]

rrrrrrrrrrrrrrrr

Loading...

Loading...