Inter-integrated circuit (I2C) interface RM0440

1920/2126 RM0440 Rev 4

41.7.5 I2C timing register (I2C_TIMINGR)

Address offset: 0x10

Reset value: 0x0000 0000

Access: No wait states

Note: This register must be configured when the I2C is disabled (PE = 0).

Note: The STM32CubeMX tool calculates and provides the I2C_TIMINGR content in the I2C

Configuration window.

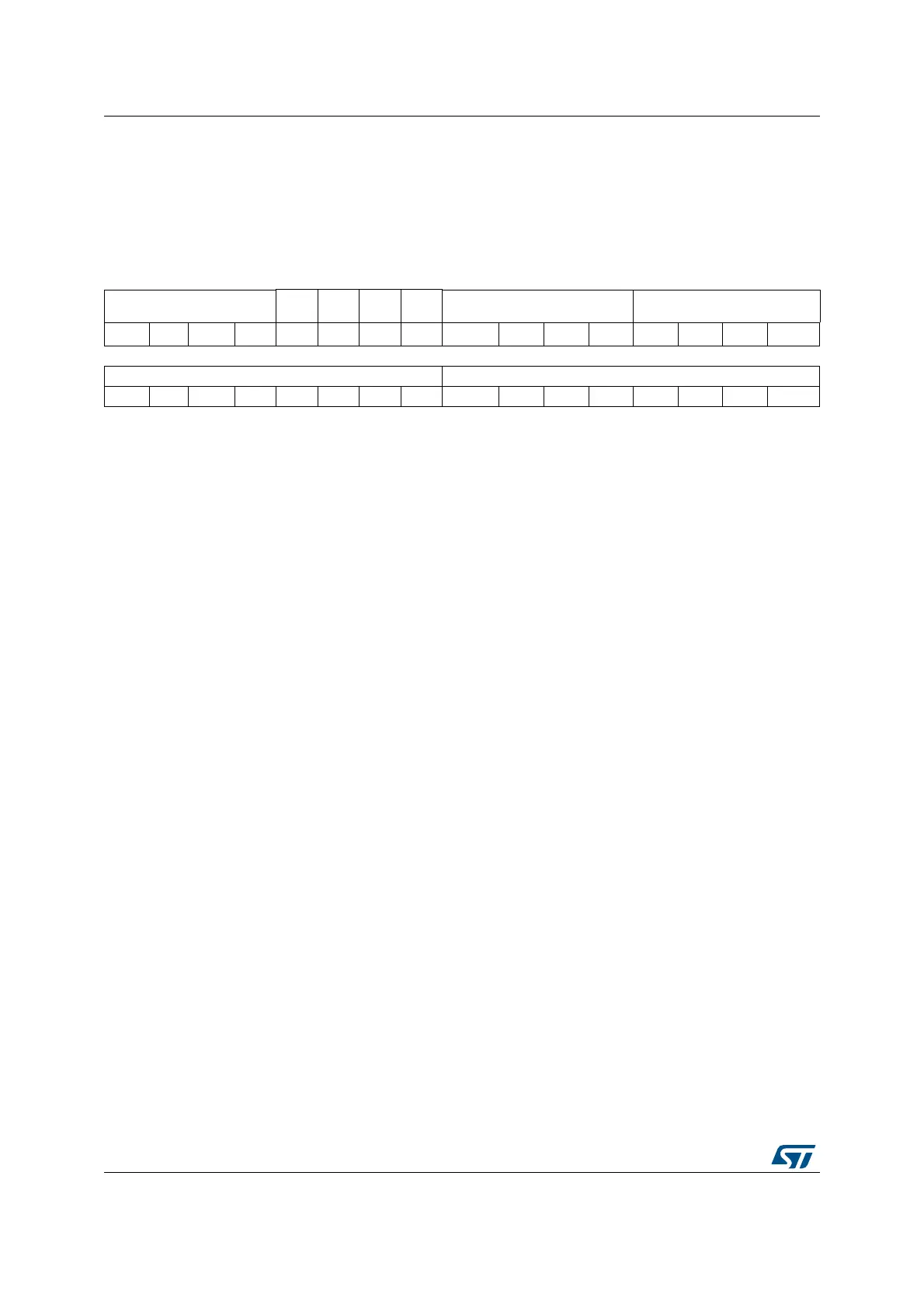

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PRESC[3:0] Res. Res. Res. Res. SCLDEL[3:0] SDADEL[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw

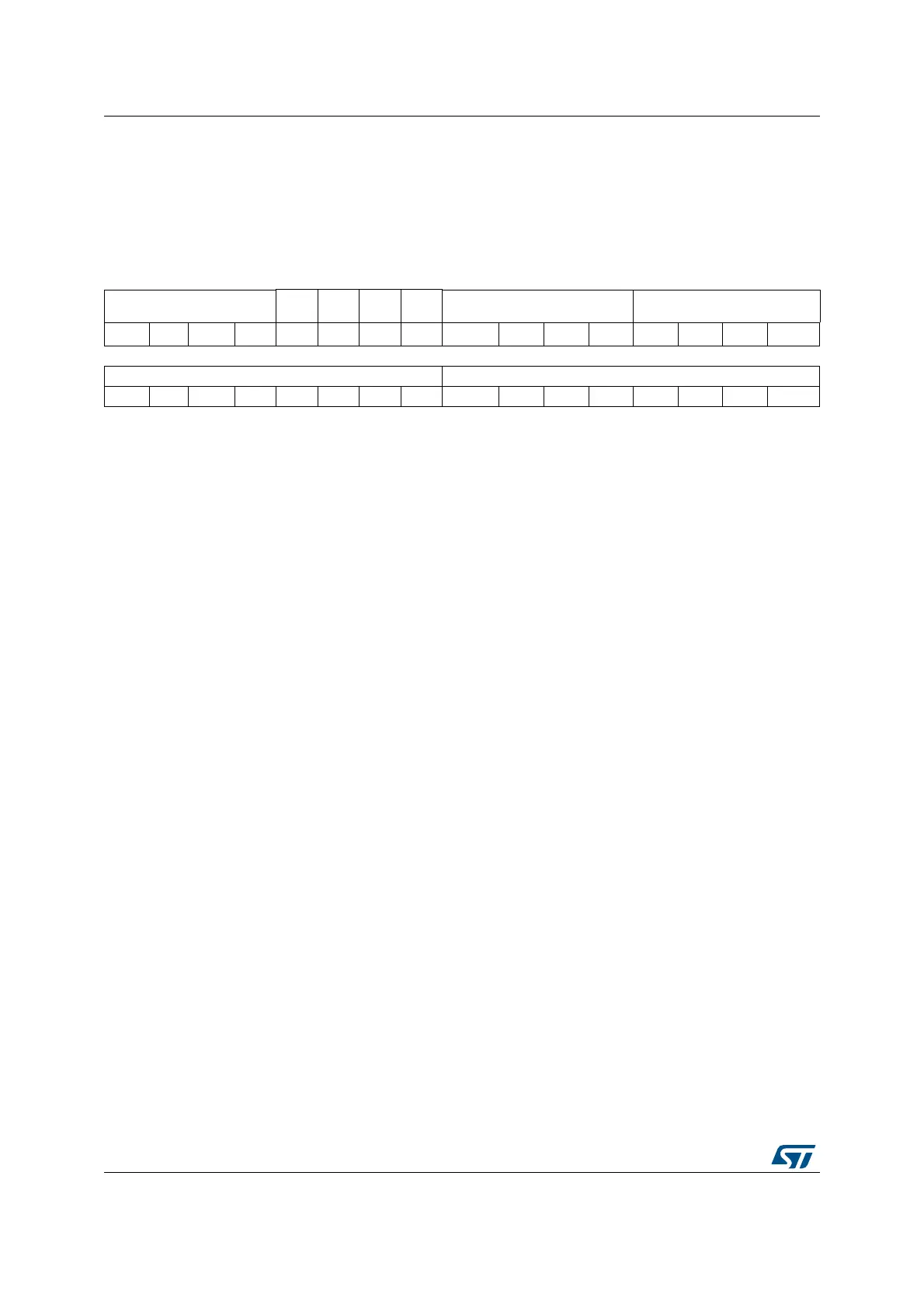

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SCLH[7:0] SCLL[7:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:28 PRESC[3:0]: Timing prescaler

This field is used to prescale I2CCLK in order to generate the clock period t

PRESC

used for

data setup and hold counters (refer to I2C timings on page 1865) and for SCL high and low

level counters (refer to I2C master initialization on page 1880).

t

PRESC

= (PRESC+1) x t

I2CCLK

Bits 27:24 Reserved, must be kept at reset value.

Bits 23:20 SCLDEL[3:0]: Data setup time

This field is used to generate a delay t

SCLDEL

between SDA edge and SCL rising edge. In

master mode and in slave mode with NOSTRETCH = 0, the SCL line is stretched low during

t

SCLDEL

.

t

SCLDEL

= (SCLDEL+1) x t

PRESC

Note: t

SCLDEL

is used to generate t

SU:DAT

timing.

Bits 19:16 SDADEL[3:0]: Data hold time

This field is used to generate the delay t

SDADEL

between SCL falling edge and SDA edge. In

master mode and in slave mode with NOSTRETCH = 0, the SCL line is stretched low during

t

SDADEL

.

t

SDADEL

= SDADEL x t

PRESC

Note: SDADEL is used to generate t

HD:DAT

timing.

Bits 15:8 SCLH[7:0]: SCL high period (master mode)

This field is used to generate the SCL high period in master mode.

t

SCLH

= (SCLH+1) x t

PRESC

Note: SCLH is also used to generate t

SU:STO

and t

HD:STA

timing.

Bits 7:0 SCLL[7:0]: SCL low period (master mode)

This field is used to generate the SCL low period in master mode.

t

SCLL

= (SCLL+1) x t

PRESC

Note: SCLL is also used to generate t

BUF

and t

SU:STA

timings.

Loading...

Loading...