Universal serial bus full-speed device interface (USB) RM0440

2038/2126 RM0440 Rev 4

Reception buffer address n (USB_ADDRn_RX)

Address offset: [USB_BTABLE] + n*8 + 4

Note: In case of double-buffered or isochronous endpoints in the OUT direction, this address

location is referred to as USB_ADDRn_RX_1.

In case of double-buffered or isochronous endpoints in the IN direction, this address location

is used for USB_ADDRn_TX_1.

Reception byte count n (USB_COUNTn_RX)

Address offset: [USB_BTABLE] + n*8 + 6

Note: In case of double-buffered or isochronous endpoints in the OUT direction, this address

location is referred to as USB_COUNTn_RX_1.

In case of double-buffered or isochronous endpoints in the IN direction, this address location

is used for USB_COUNTn_TX_1.

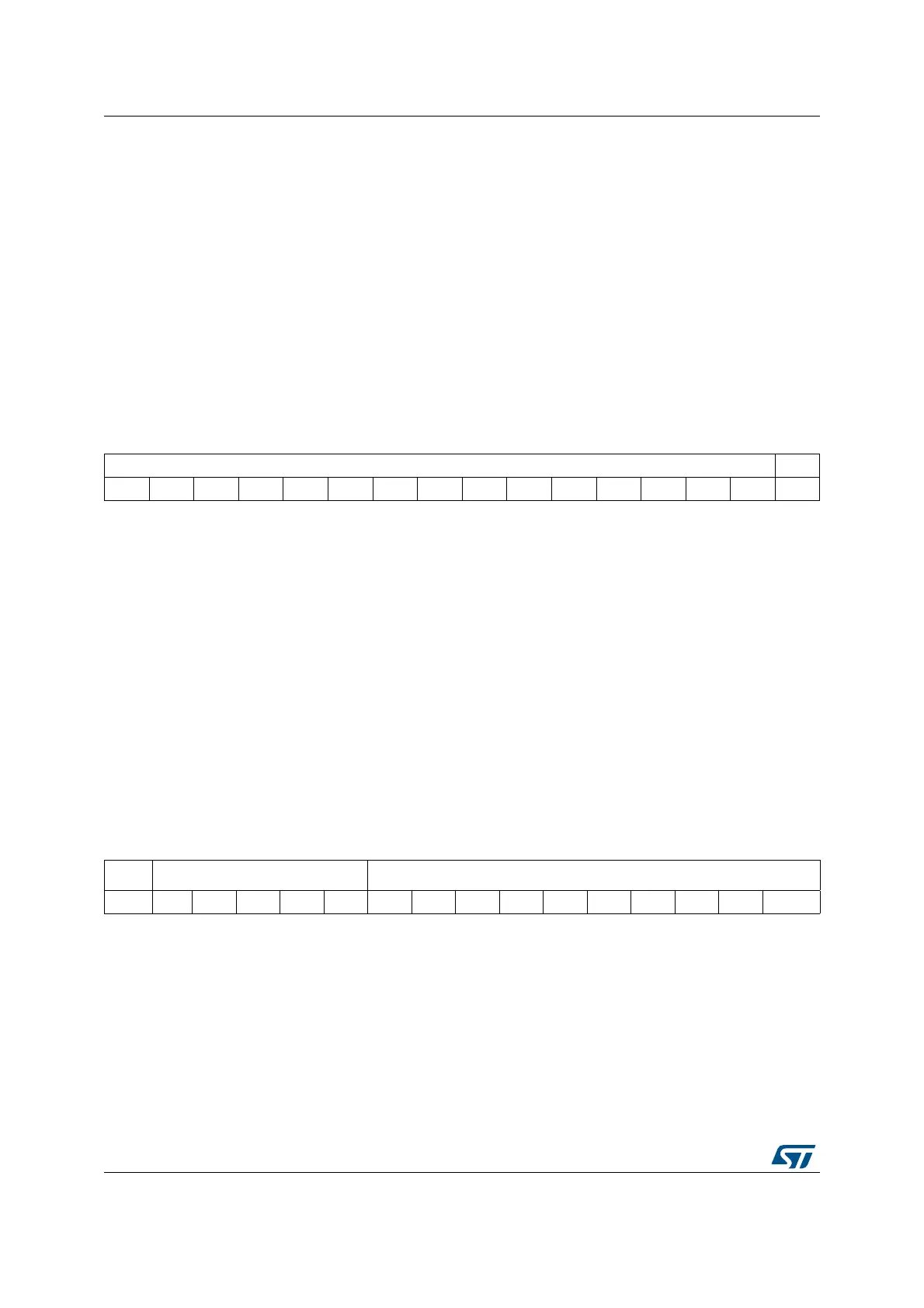

This table location is used to store two different values, both required during packet

reception. The most significant bits contains the definition of allocated buffer size, to allow

buffer overflow detection, while the least significant part of this location is written back by the

USB peripheral at the end of reception to give the actual number of received bytes. Due to

the restrictions on the number of available bits, buffer size is represented using the number

of allocated memory blocks, where block size can be selected to choose the trade-off

between fine-granularity/small-buffer and coarse-granularity/large-buffer. The size of

allocated buffer is a part of the endpoint descriptor and it is normally defined during the

Bits 15:10 These bits are not used since packet size is limited by USB specifications to 1023 bytes. Their

value is not considered by the USB peripheral.

Bits 9:0 COUNTn_TX[9:0]: Transmission byte count

These bits contain the number of bytes to be transmitted by the endpoint associated with the

USB_EPnR register at the next IN token addressed to it.

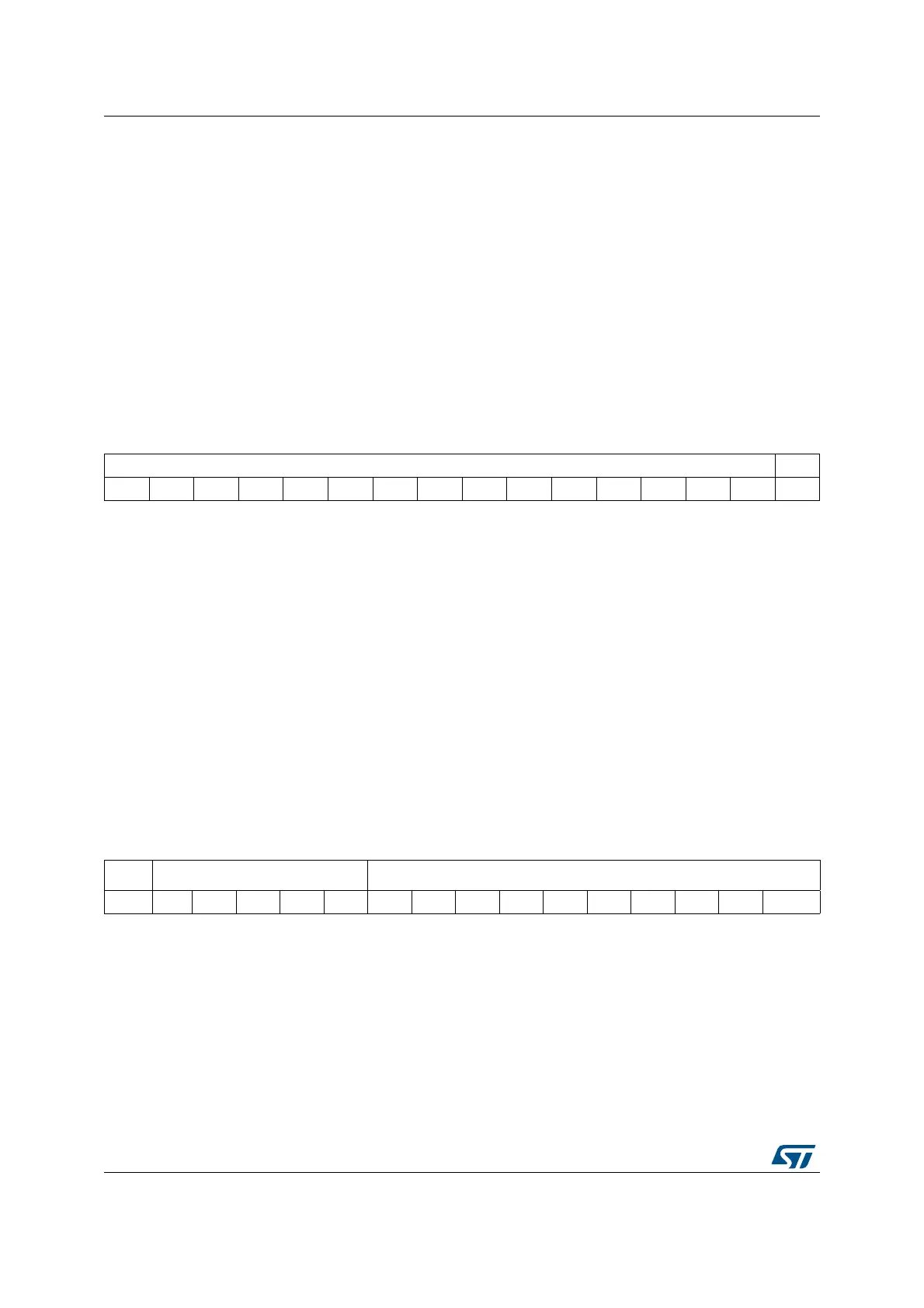

1514131211109876543210

ADDRn_RX[15:1] -

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw -

Bits 15:1 ADDRn_RX[15:1]: Reception buffer address

These bits point to the starting address of the packet buffer, which will contain the data

received by the endpoint associated with the USB_EPnR register at the next OUT/SETUP

token addressed to it.

Bit 0 This bit must always be written as ‘0 since packet memory is half-word wide and all packet

buffers must be half-word aligned.

151413121110987654321 0

BLSIZE NUM_BLOCK[4:0] COUNTn_RX[9:0]

rwrwrwrwrwrwrrrrrrrrr r

Loading...

Loading...