RM0440 Rev 4 255/2126

RM0440 Power control (PWR)

271

6.4 PWR registers

The peripheral registers can be accessed by half-words (16-bit) or words (32-bit).

6.4.1 Power control register 1 (PWR_CR1)

Address offset: 0x00

Reset value: 0x0000 0200. This register is reset after wakeup from Standby mode.

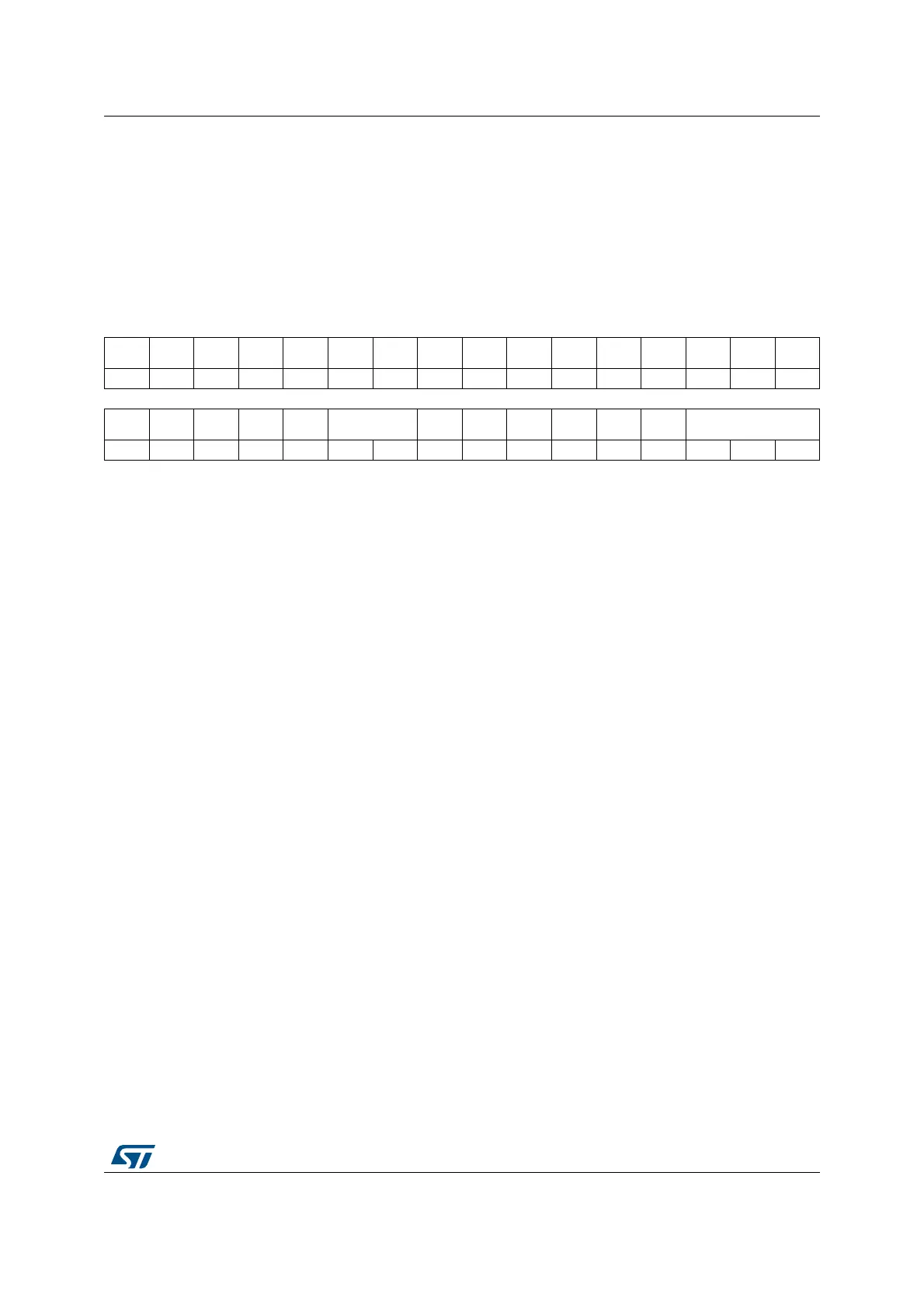

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. LPR Res. Res. Res. VOS[1:0] DBP Res. Res. Res. Res. Res. LPMS[2:0]

rw rw rw rw rw rw rw

Bits 31:15 Reserved, must be kept at reset value.

Bit 14 LPR: Low-power run

When this bit is set, the regulator is switched from main mode (MR) to low-power mode

(LPR).

Bits 13:11 Reserved, must be kept at reset value.

Bits 10:9 VOS: Voltage scaling range selection

00: Cannot be written (forbidden by hardware)

01: Range 1

10: Range 2

11: Cannot be written (forbidden by hardware)

Bit 8 DBP: Disable backup domain write protection

In reset state, the RTC and backup registers are protected against parasitic write access.

This bit must be set to enable write access to these registers.

0: Access to RTC and Backup registers disabled

1: Access to RTC and Backup registers enabled

Bits 7:3 Reserved, must be kept at reset value.

Bits 2:0 LPMS[2:0]: Low-power mode selection

These bits select the low-power mode entered when CPU enters the deepsleep mode.

000: Stop 0 mode

001: Stop 1 mode

010: Reserved

011: Standby mode

1xx: Shutdown mode

Note: In Standby mode, SRAM2 can be preserved or not, depending on RRS bit configuration

in PWR_CR3.

Loading...

Loading...