RM0440 Rev 4 289/2126

RM0440 Reset and clock control (RCC)

338

7.4 RCC registers

7.4.1 Clock control register (RCC_CR)

Address offset: 0x00

Reset value: 0x0000 0063

HSEBYP is not affected by reset.

Access: no wait state, word, half-word and byte access

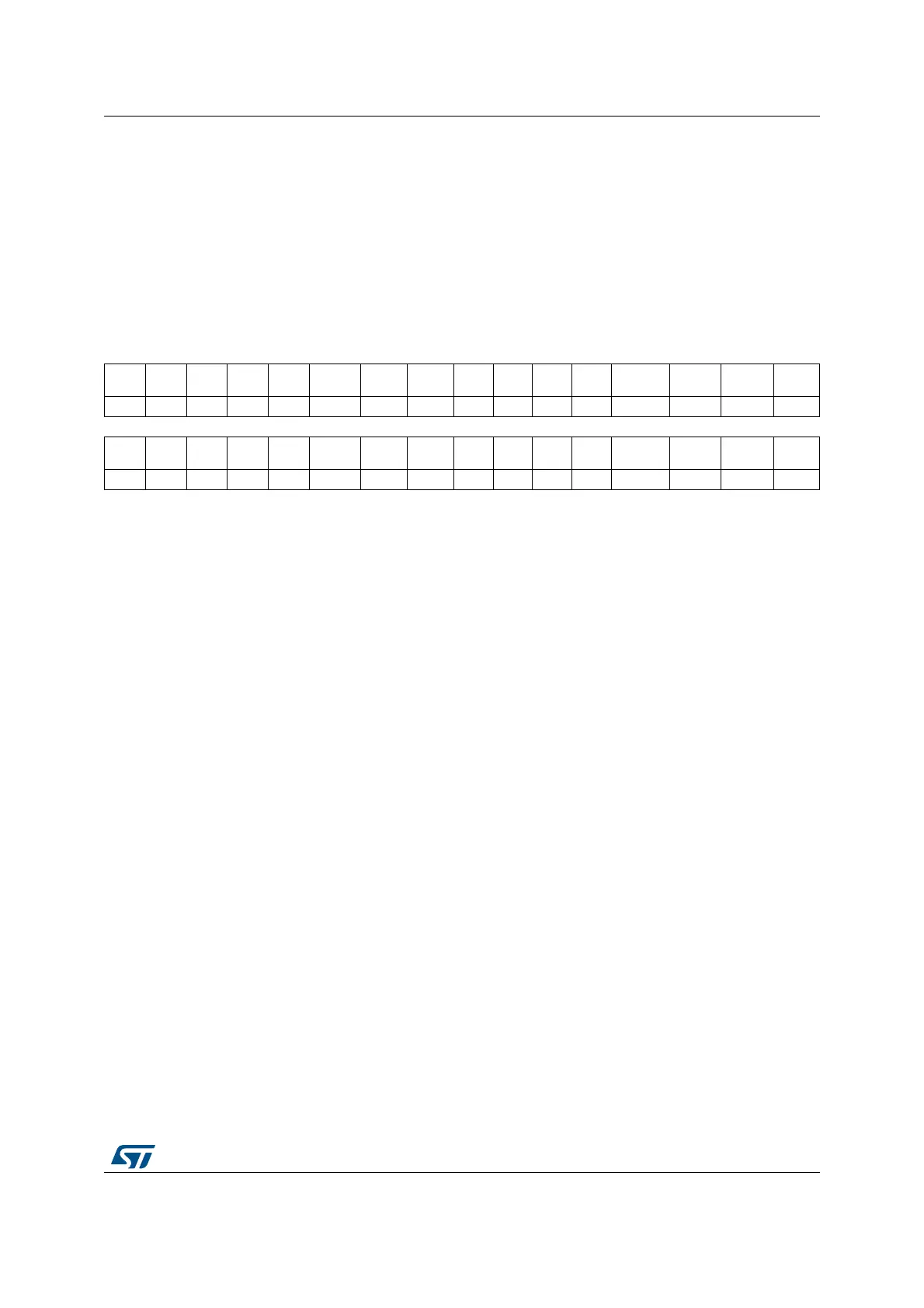

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res.

PLL

RDY

PLLON Res. Res. Res. Res. CSSON HSEBYP HSERDY HSEON

rrw rs rw r rw

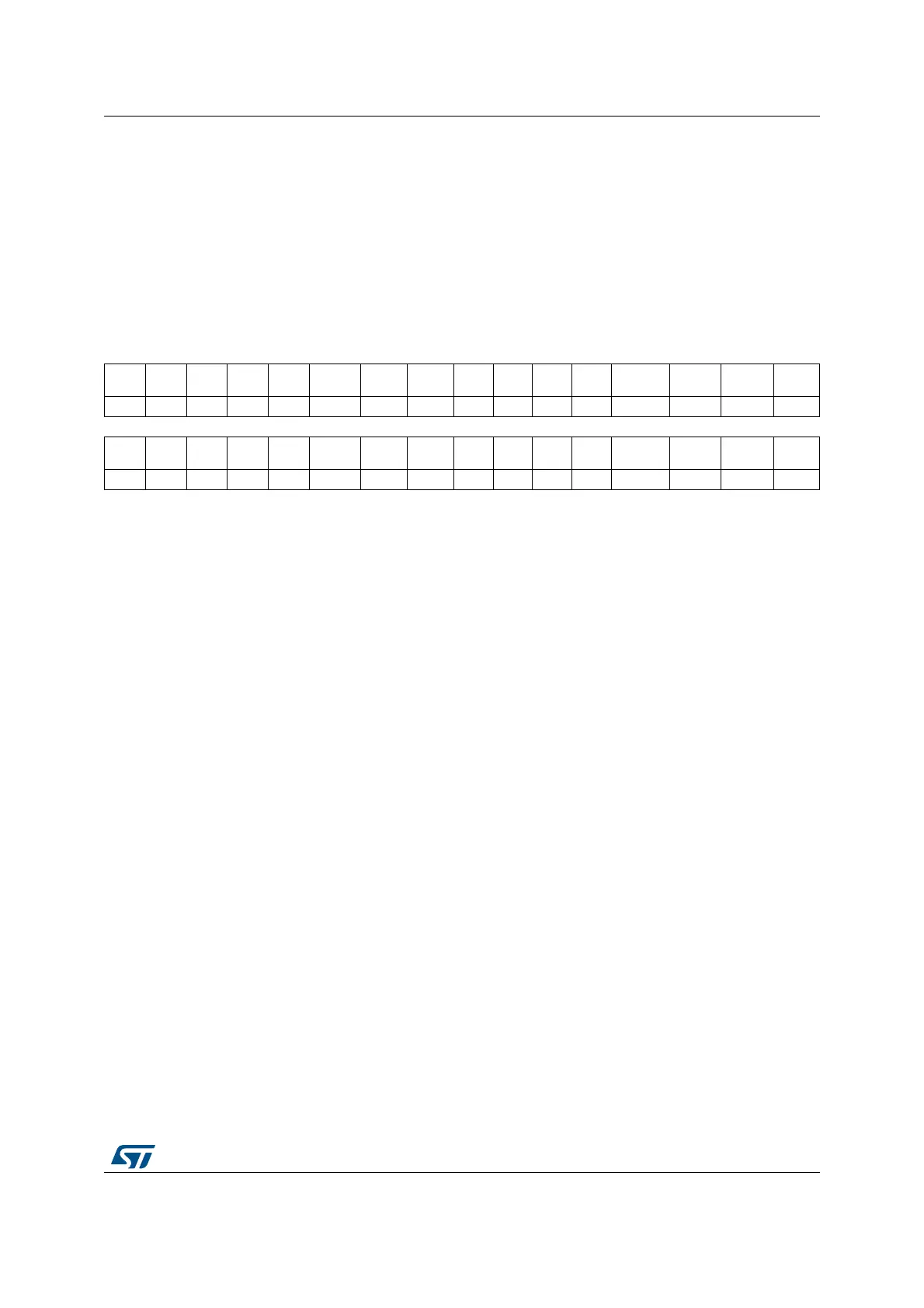

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res.

HSI

RDY

HSI

KERON

HSION Res. Res. Res. Res. Res. Res. Res. Res.

rrwrw

Bits 31:26 Reserved, must be kept at reset value.

Bit 25 PLLRDY: Main PLL clock ready flag

Set by hardware to indicate that the main PLL is locked.

0: PLL unlocked

1: PLL locked

Bit 24 PLLON: Main PLL enable

Set and cleared by software to enable the main PLL.

Cleared by hardware when entering Stop, Standby or Shutdown mode. This bit cannot be

reset if the PLL clock is used as the system clock.

0: PLL OFF

1: PLL ON

Bits 23:20 Reserved, must be kept at reset value.

Bit 19 CSSON: Clock security system enable

Set by software to enable the clock security system. When CSSON is set, the clock detector

is enabled by hardware when the HSE oscillator is ready, and disabled by hardware if a HSE

clock failure is detected. This bit is set only and is cleared by reset.

0: Clock security system OFF (clock detector OFF)

1: Clock security system ON (Clock detector ON if the HSE oscillator is stable, OFF if not).

Bit 18 HSEBYP: HSE crystal oscillator bypass

Set and cleared by software to bypass the oscillator with an external clock. The external

clock must be enabled with the HSEON bit set, to be used by the device. The HSEBYP bit

can be written only if the HSE oscillator is disabled.

0: HSE crystal oscillator not bypassed

1: HSE crystal oscillator bypassed with external clock

Bit 17 HSERDY: HSE clock ready flag

Set by hardware to indicate that the HSE oscillator is stable.

0: HSE oscillator not ready

1: HSE oscillator ready

Note: Once the HSEON bit is cleared, HSERDY goes low after 6 HSE clock cycles.

Loading...

Loading...