DMA request multiplexer (DMAMUX) RM0440

438/2126 RM0440 Rev 4

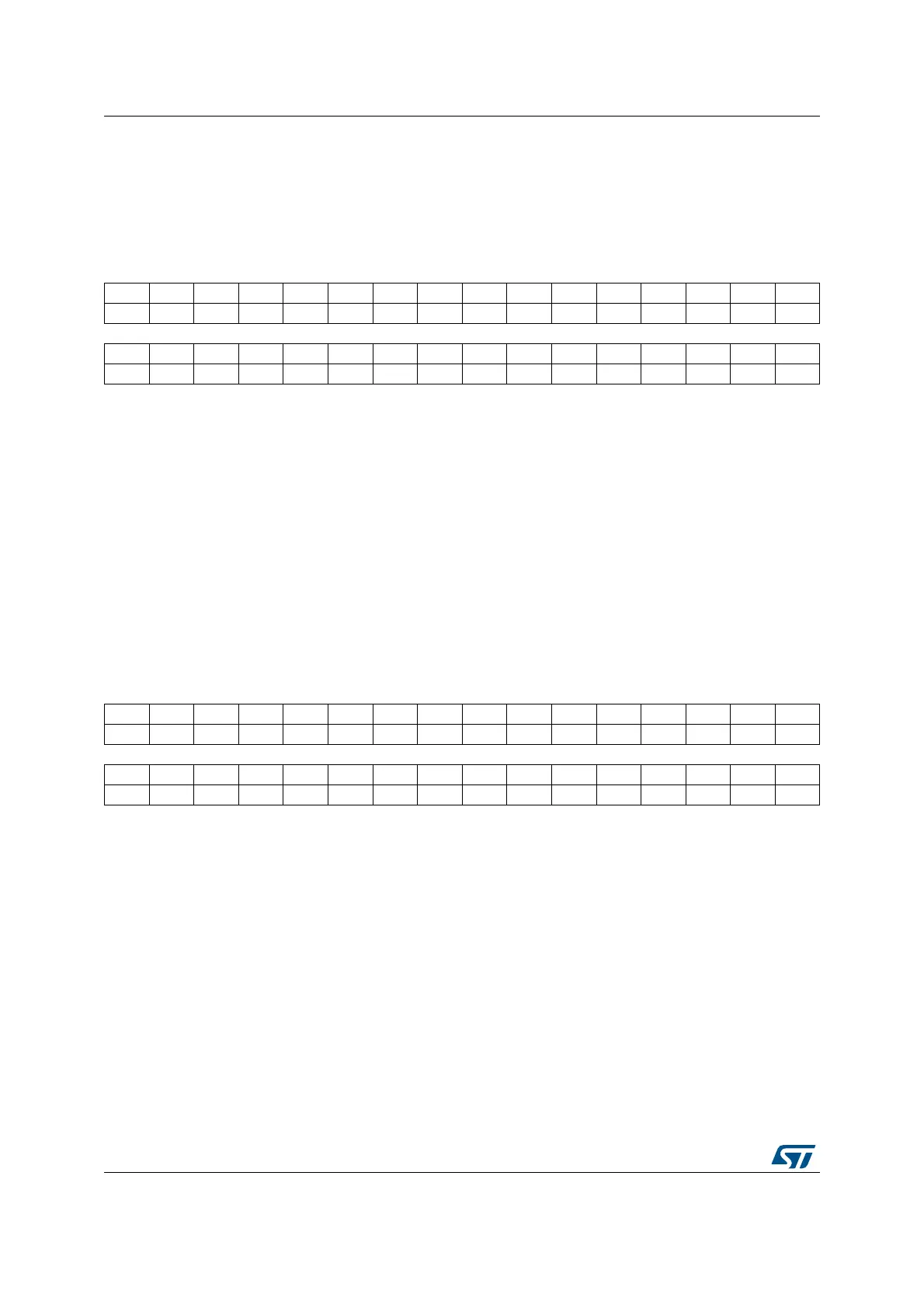

13.6.5 DMAMUX request generator interrupt status register

(DMAMUX_RGSR)

Address offset: 0x140

Reset value: 0x0000 0000

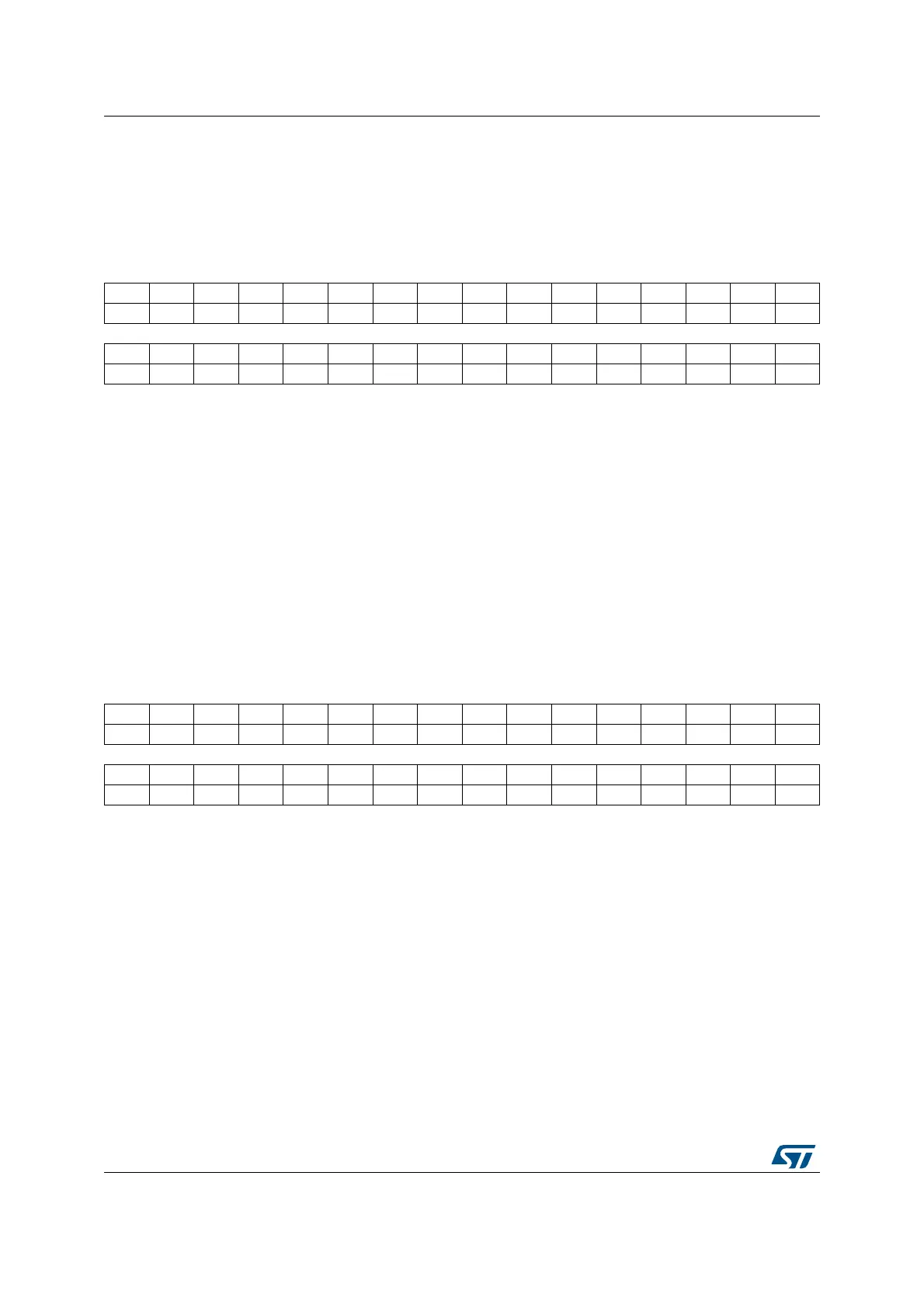

13.6.6 DMAMUX request generator interrupt clear flag register

(DMAMUX_RGCFR)

Address offset: 0x144

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. OF3 OF2 OF1 OF0

rrrr

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 OF[3:0]: Trigger overrun event flag

The flag is set when a new trigger event occurs on DMA request generator channel x, before

the request counter underrun (the internal request counter programmed via the GNBREQ

field of the DMAMUX_RGxCR register).

The flag is cleared by writing 1 to the corresponding COFx bit in the DMAMUX_RGCFR

register.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. COF3 COF2 COF1 COF0

wwww

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 COF[3:0]: Clear trigger overrun event flag

Writing 1 in each bit clears the corresponding overrun flag OFx in the DMAMUX_RGSR

register.

Loading...

Loading...