Digital-to-analog converter (DAC) RM0440

770/2126 RM0440 Rev 4

22.7.23 DAC sawtooth mode register (DAC_STMODR)

Address offset: 0x60

Reset value: 0x0000 0000

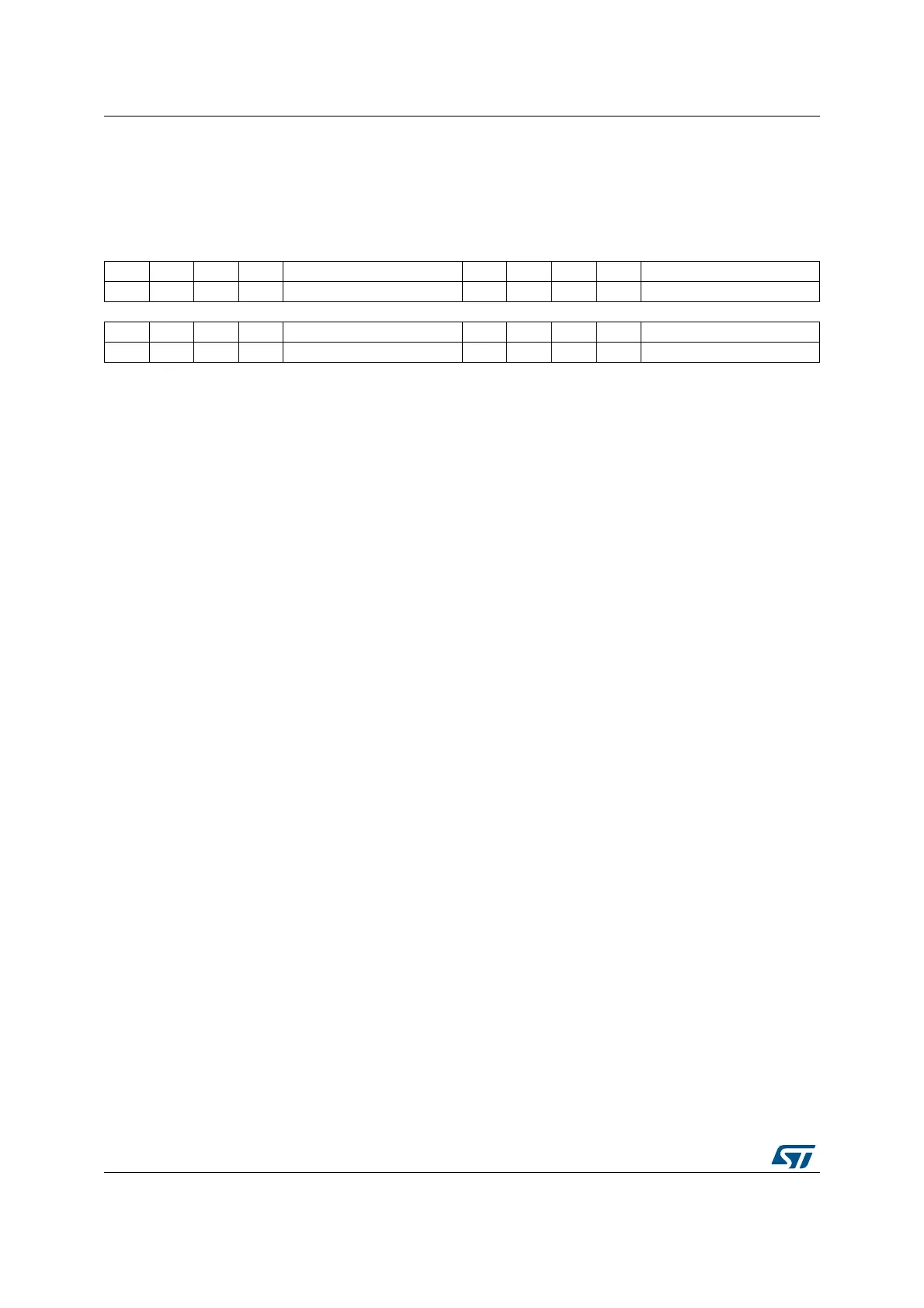

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. STINCTRIGSEL2[3:0] Res. Res. Res. Res. STRSTTRIGSEL2[3:0]

rw rw

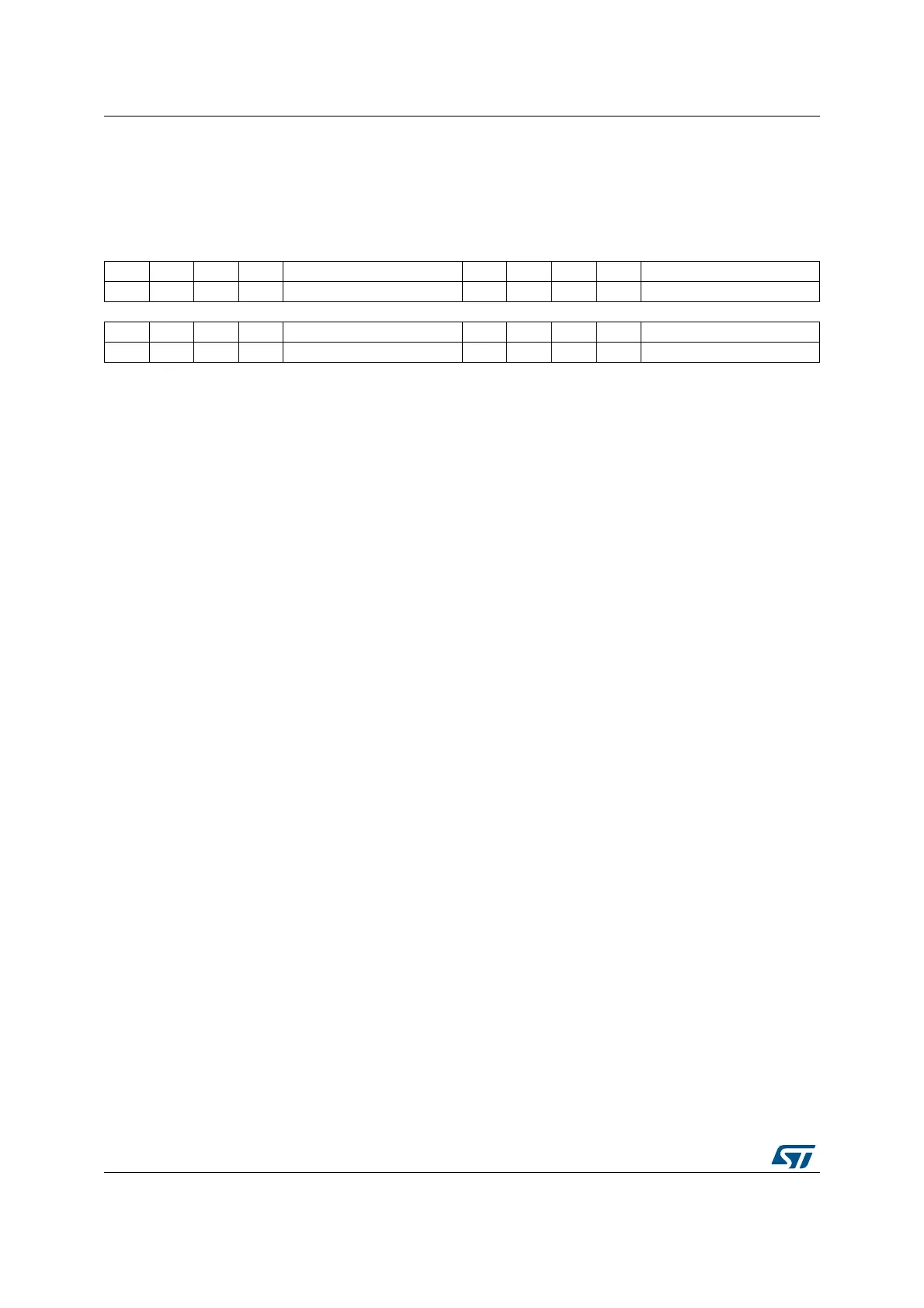

1514131211109876543210

Res. Res. Res. Res. STINCTRIGSEL1[3:0] Res. Res. Res. Res. STRSTTRIGSEL1[3:0]

rw rw

Bits 31:28

Reserved, must be kept at reset value.

Bits 27:24 STINCTRIGSEL2[3:0]: DAC channel2 sawtooth increment trigger selection

Refer to the trigger selection tables in Section 22.4.2: DAC pins and internal signals for

details on trigger configuration and mapping.

0000: SWTRIGB2

0001: dac_inc_ch2_trg1

....

1111: dac_inc_ch2_trg15

Note: These bits are available only on dual-channel DACs. Refer to Section 22.3: DAC

implementation.

Bits 19:16 STRSTTRIGSEL2[3:0]: DAC channel2 sawtooth reset trigger selection

Refer to the trigger selection tables in Section 22.4.2: DAC pins and internal signals for

details on trigger configuration and mapping.

0000: SWTRIGB2

0001: dac_ch2_trg1

....

1111: dac_ch2_trg15

The mapping is the same as for TSEL2[3:0].

Note: These bits are available only on dual-channel DACs. Refer to Section 22.3: DAC

implementation.

Bits 15:12

Reserved, must be kept at reset value.

Loading...

Loading...