High-resolution timer (HRTIM) RM0440

964/2126 RM0440 Rev 4

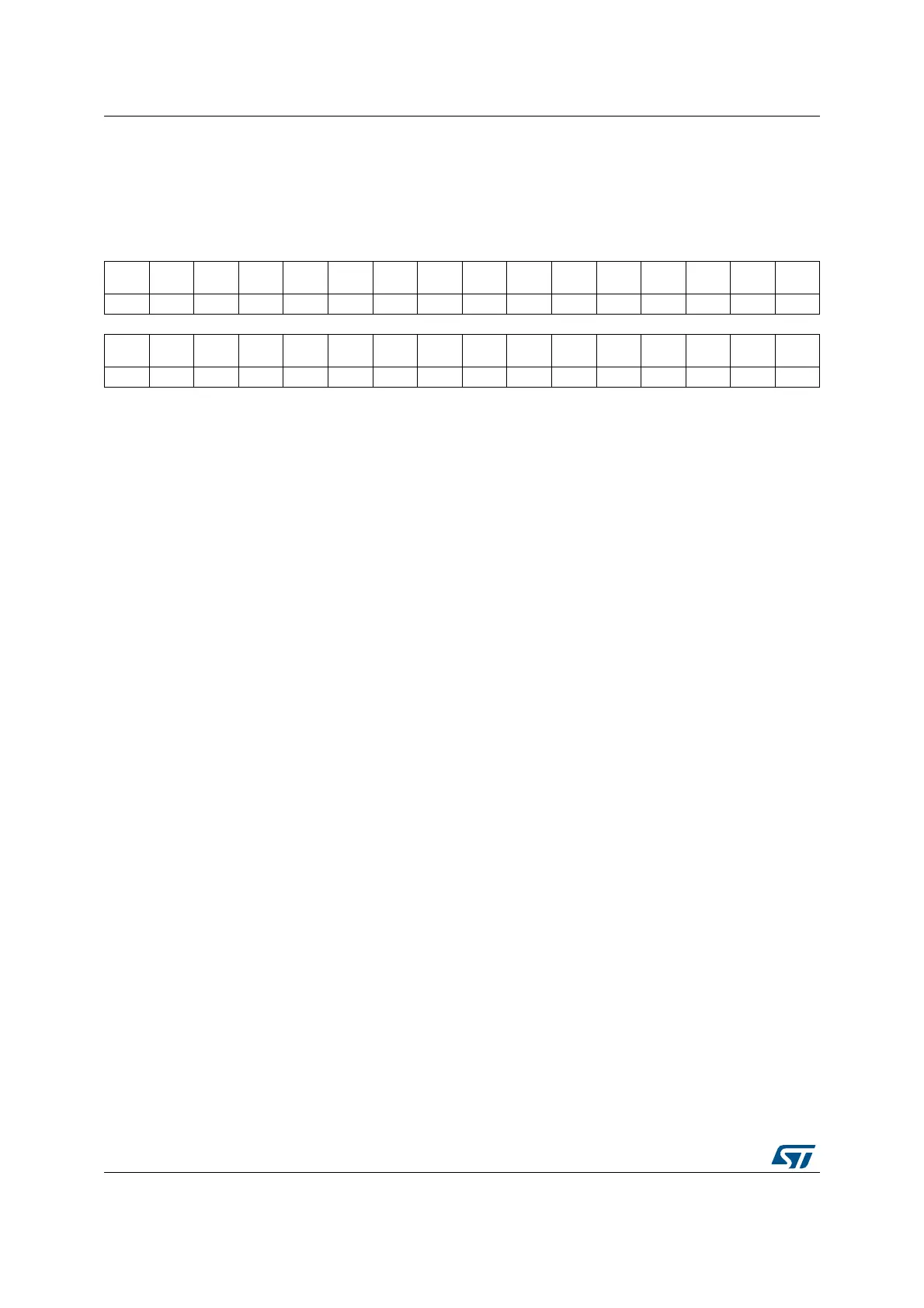

27.5.4 HRTIM master timer DMA interrupt enable register (HRTIM_MDIER)

Address offset: 0x00C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res.

MUPD

DE

SYNCD

E

MREP

DE

MCMP

4DE

MCMP

3DE

MCMP

2DE

MCMP

1DE

rw rw rw rw rw rw rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res.

MUPDI

E

SYNCI

E

MREPI

E

MCMP

4IE

MCMP

3IE

MCMP

2IE

MCMP

1IE

rw rw rw rw rw rw rw

Bits 31:23 Reserved, must be kept at reset value.

Bit 22 MUPDDE: Master update DMA request enable

This bit is set and cleared by software to enable/disable the master update DMA requests.

0: Master update DMA request disabled

1: Master update DMA request enabled

Bit 21 SYNCDE: Sync input DMA request enable

This bit is set and cleared by software to enable/disable the sync input DMA requests.

0: Sync input DMA request disabled

1: Sync input DMA request enabled

Bit 20 MREPDE: Master repetition DMA request enable

This bit is set and cleared by software to enable/disable the master timer repetition DMA requests.

0: Repetition DMA request disabled

1: Repetition DMA request enabled

Bit 19 MCMP4DE: Master compare 4 DMA request enable

Refer to MCMP1DE description

Bit 18 MCMP3DE: Master compare 3 DMA request enable

Refer to MCMP1DE description

Bit 17 MCMP2DE: Master compare 2 DMA request enable

Refer to MCMP1DE description

Bit 16 MCMP1DE: Master compare 1 DMA request enable

This bit is set and cleared by software to enable/disable the master timer compare 1 DMA requests.

0: Compare 1 DMA request disabled

1: Compare 1 DMA request enabled

Bits 15:6 Reserved, must be kept at reset value.

Bit 6 MUPDIE: Master update interrupt enable

This bit is set and cleared by software to enable/disable the master timer registers update interrupts

0: Master update interrupts disabled

1: Master update interrupts enabled

Bit 5 SYNCIE: Sync input interrupt enable

This bit is set and cleared by software to enable/disable the sync input interrupts

0: Sync input interrupts disabled

1: Sync input interrupts enabled

Loading...

Loading...