RM0440 Rev 4 1031/2126

RM0440 High-resolution timer (HRTIM)

1083

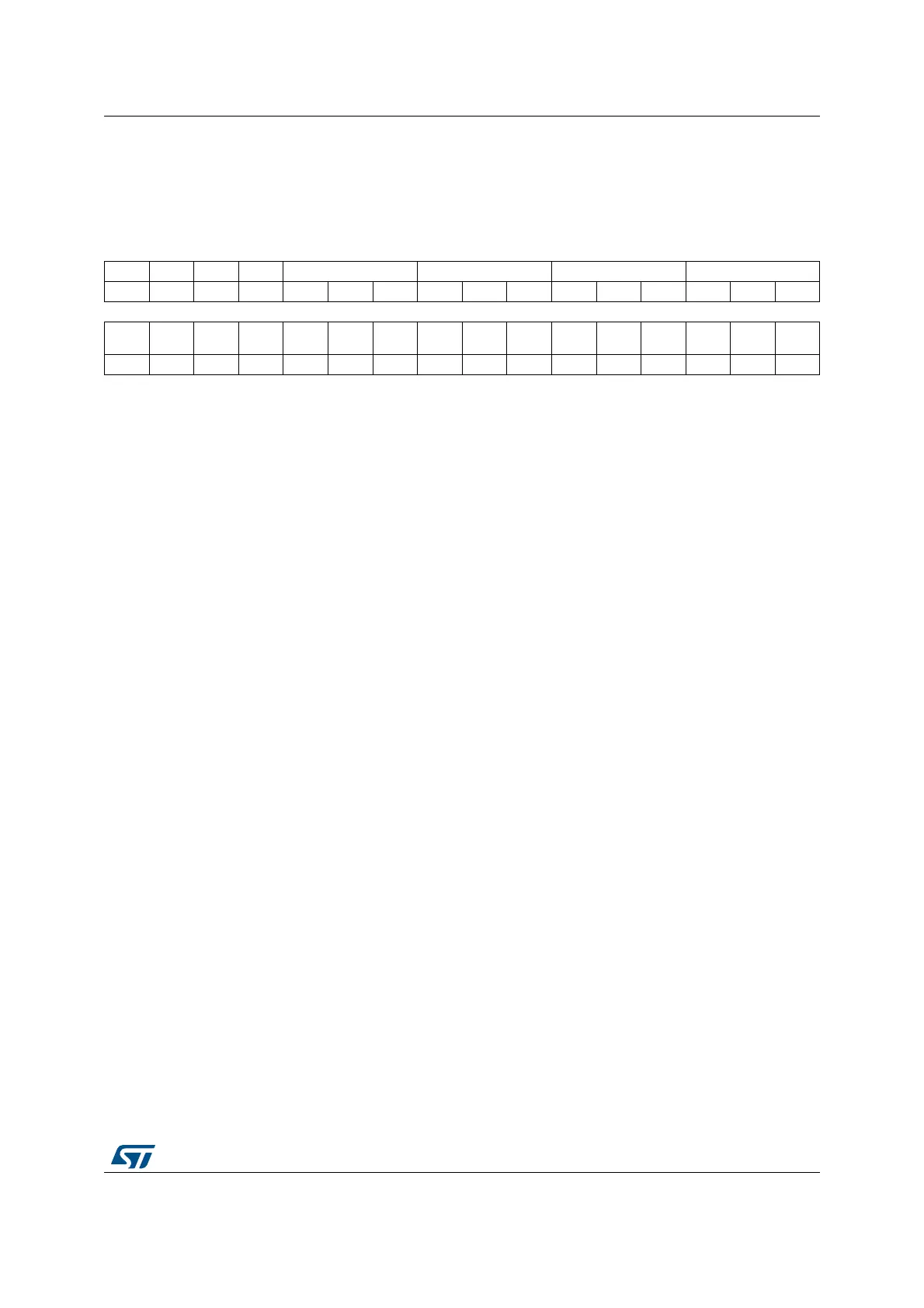

27.5.51 HRTIM control register 1 (HRTIM_CR1)

Address offset: 0x380

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. AD4USRC[2:0] AD3USRC[2:0] AD2USRC[2:0] AD1USRC[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw

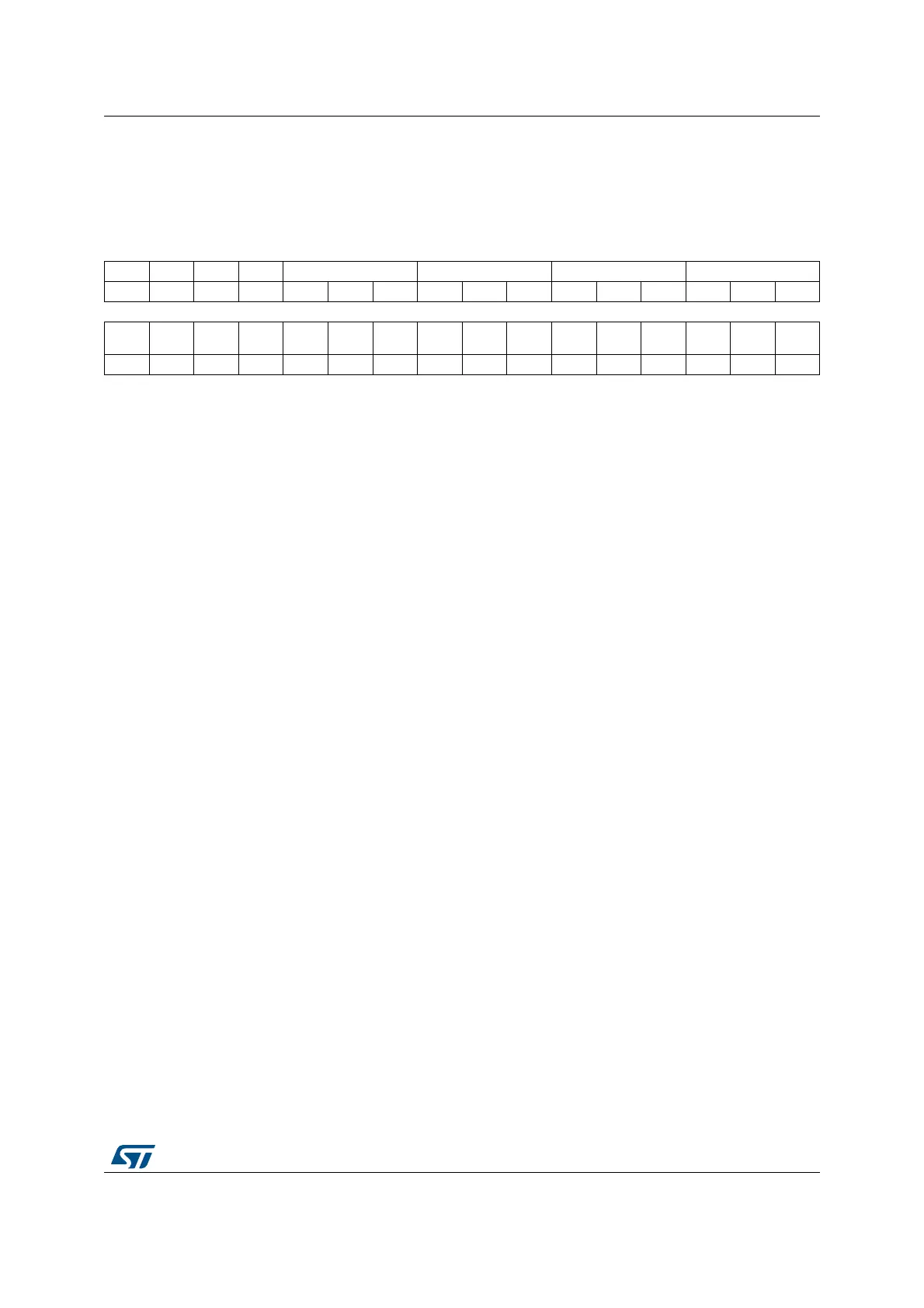

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res.

TF

UDIS

TE

UDIS

TD

UDIS

TC

UDIS

TB

UDIS

TA

UDIS

MUDIS

rw rw rw rw rw rw rw

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:25 AD4USRC[2:0]: ADC trigger 4 update source

Refer to AD1USRC[2:0] description.

Bits 24:22 AD3USRC[2:0]: ADC trigger 3 update source

Refer to AD1USRC[2:0] description.

Bits 21:19 AD2USRC[2:0]: ADC trigger 2 update source

Refer to AD1USRC[2:0] description.

Bits 18:16 AD1USRC[2:0]: ADC trigger 1 update source

These bits define the source which triggers the update of the HRTIM_ADC1R register (transfer from

preload to active register). It only defines the source timer. The precise condition is defined within the

timer itself, in HRTIM_MCR or HRTIM_TIMxCR.

000: Master timer

001: Timer A

010: Timer B

011: Timer C

100: Timer D

101: Timer E

110: Timer F

111: Reserved

Bits 15:7 Reserved, must be kept at reset value.

Bit 6 TFUDIS: Timer F update disable

Refer to TAUDIS description.

Bit 5 TEUDIS: Timer E update disable

Refer to TAUDIS description

Bit 4 TDUDIS: Timer D update disable

Refer to TAUDIS description.

Bit 3 TCUDIS: Timer C update disable

Refer to TAUDIS description.

Loading...

Loading...