RM0440 Rev 4 1041/2126

RM0440 High-resolution timer (HRTIM)

1083

27.5.59 HRTIM burst mode control register (HRTIM_BMCR)

Address offset: 0x3A0

Reset value: 0x0000 0000

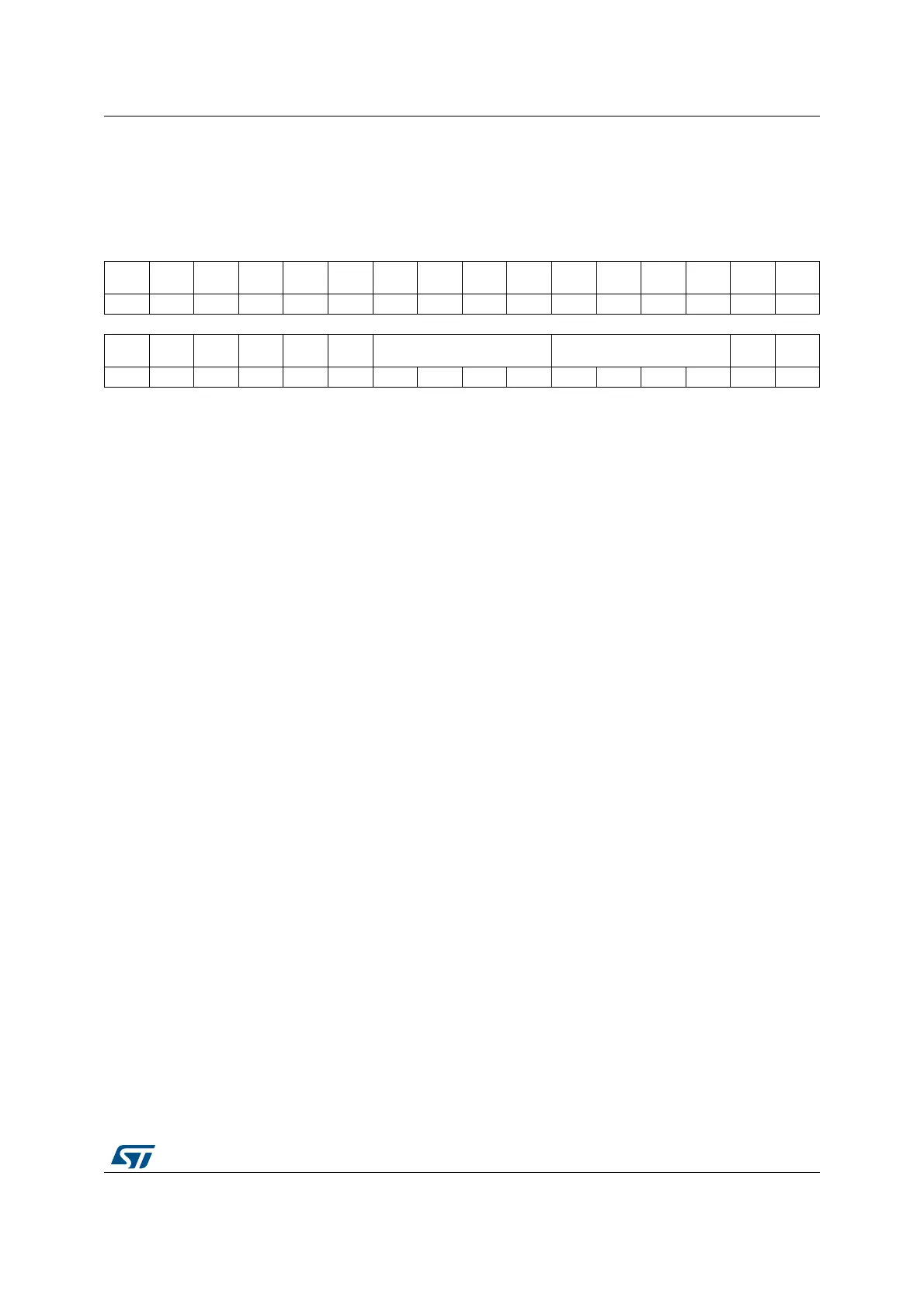

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

BMSTA

T

Res. Res. Res. Res. Res. Res. Res. Res. TFBM TEBM TDBM TCBM TBBM TABM MTBM

rc_w0 rw rw rw rw rw rw rw

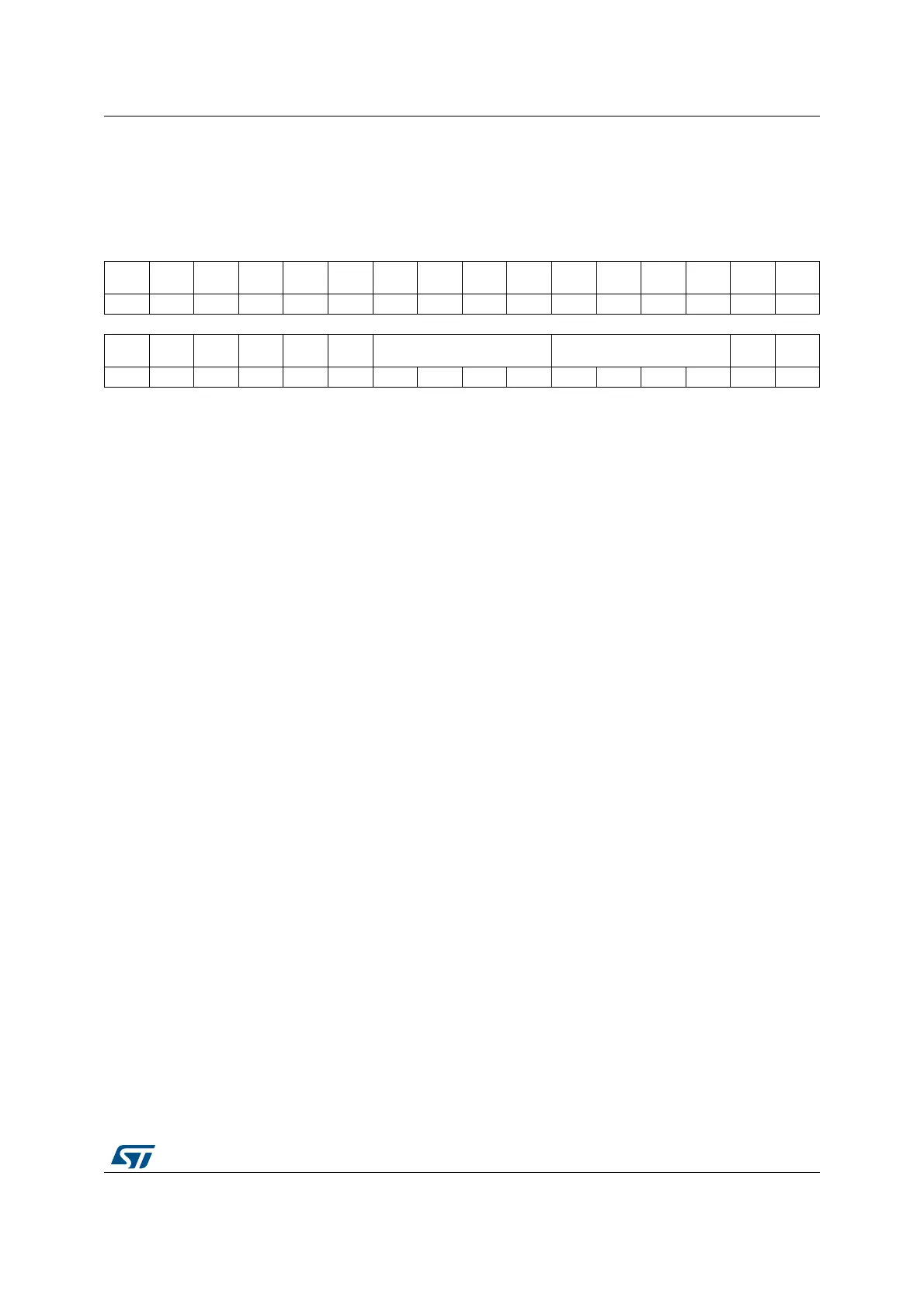

1514131211109876543210

Res. Res. Res. Res. Res.

BMPR

EN

BMPRSC[3:0] BMCLK[3:0] BMOM BME

rw rw rw rw rw rw rw rw rw rw rw

Bit 31 BMSTAT: Burst mode status

This bit gives the current operating state.

0: Normal operation

1: Burst operation on-going. Writing this bit to 0 causes a burst mode early termination.

Bits 30:23 Reserved, must be kept at reset value.

Bit 22 TFBM: Timer F burst mode

Refer to TABM description.

Bit 21 TEBM: Timer E burst mode

Refer to TABM description.

Bit 20 TDBM: Timer D burst mode

Refer to TABM description.

Bit 19 TCBM: Timer C burst mode

Refer to TABM description.

Bit 18 TBBM: Timer B burst mode

Refer to TABM description.

Bit 17 TABM: Timer A burst mode

This bit defines how the timer behaves during a burst mode operation. This bitfield cannot be

changed while the burst mode is enabled.

0: TA counter clock is maintained and the timer operates normally

1: TA counter clock is stopped and the counter is reset

Note: This bit must not be set when the balanced idle mode is active (DLYPRT[2:0] = 0x11).

Bit 16 MTBM: Master timer burst mode

This bit defines how the timer behaves during a burst mode operation. This bitfield cannot be

changed while the burst mode is enabled.

0: Master Timer counter clock is maintained and the timer operates normally

1: Master Timer counter clock is stopped and the counter is reset

Bits 15:11 Reserved, must be kept at reset value.

Bit 10 BMPREN: Burst mode preload enable

This bit enables the registers preload mechanism and defines whether a write access into a preload-

able register (HRTIM_BMCMPR, HRTIM_BMPER) is done into the active or the preload register.

0: Preload disabled: the write access is directly done into active registers

1: Preload enabled: the write access is done into preload registers

Loading...

Loading...